# PARAMETERIZED HIGH PERFORMANCE CORDIC PROCESSOR ARCHITECTURES FOR FPGAS ARCHITECTURES DE PROCESSEURS CORDIC À HAUTE PERFORMANCE AVEC PARAMÉTRAGE POUR FPGAS

A Thesis Submitted to the Faculty of the Royal Military College of Canada

by

Guillaume Gilbert, B.Eng. Captain

In Partial Fulfillment of the Requirements for the Degree of

Master of Applied Science in Computer Engineering

August 2005

©Copyright 2005. This thesis may be used within the Department of National Defence but copyright for open publication remains the property of the author.

Library and Archives Canada

Branch

Published Heritage Direction du

395 Wellington Street Ottawa ON K1A 0N4 Canada 395, rue Wellington Ottawa ON K1A 0N4 Canada

Patrimoine de l'édition

Bibliothèque et

Archives Canada

Your file Votre référence ISBN: 978-0-494-36473-4 Our file Notre référence ISBN: 978-0-494-36473-4

## NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

## AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# **ACKNOWLEDGMENTS**

I sincerely and gratefully acknowledge the highly valued assistance, guidance and encouragement given to me by Dr. Dhamin Al-Khalili and Dr. Côme Rozon throughout the entire duration of this thesis. Their patience and understanding have helped a great deal through the more difficult times encountered during the course of this work.

I would also like to thank my dear wife Marie-Chantale, who had to endure many hardships to ensure that this work was completed.

#### ABSTRACT

Gilbert, Guillaume, M.A.Sc. (Computer Engineering). Royal Military College Of Canada. August 2005. Parameterized High Performance CORDIC Processor Architectures for FPGAs.

Supervisors: Dr. Dhamin Al-Khalili, Dr. Côme Rozon.

The COordinate Rotation Digital Computer (CORDIC) performs general vector rotation in the 2D plane in the circular, linear and hyperbolic coordinate systems. Its strength lies in its ability to perform various elementary functions with a relatively simple hardware implementation. The CORDIC algorithm is highly versatile, and it has been used extensively in a broad range of applications, including Digital Signal Processing, 3D Computer Graphics, Wireless Receivers, Matrix Algebra and Robotics, to name only a few.

Modern applications have ever increasing processing requirements and demand low power consumption. In order to provide the required computing power for such applications, there has been a shift from software to specialized hardware. The need for smaller devices across a wide range of applications has also been a major driving force in the proliferation of hardware solutions. This has led to the integration of entire systems on a single chip. In addition, economic considerations have made the Field Programmable Gate Array (FPGA) an important target platform, since its development costs are much lower than those required for a custom Application Specific Integrated Circuit (ASIC).

This thesis presents the development of several different types of CORDIC processing elements specifically optimized for FPGA implementation, and examines the area-performance trade-offs for each. In order to quickly generate these different processing elements, an automatic code generation tool has been developped. These CORDIC implementations can be used in a wide variety of applications, and are particularly well suited for System on Chip (SoC) designs.

# RÉSUMÉ

Gilbert, Guillaume, M.Sc.A. (Génie Informatique). Collège Militaire Royal du Canada. Août 2005. Architecture de processeurs CORDIC à haute performance avec paramétrage pour FPGAs.

Superviseurs: Dr. Dhamin Al-Khalili, Dr. Côme Rozon.

Les champs d'applications modernes requièrent une grande rapidité du traitement des données, tout en exigeant une basse consommation de puissance. Afin de fournir la puissance de calcul requise dans de telles circonstances, il y a eu ces dernières années une transition des systèmes logiciels vers les systèmes matériels. La nécessité d'avoir des appareils de petite taille pour bon nombre d'applications a également contribué à la prolifération des systèmes matériels. Ceci a mené à l'intégration de systèmes entiers sur une seule puce. De plus, l'aspect économique a fait du réseau prédiffusé programmable par l'utilisateur (FPGA en anglais) une plateforme de choix pour les dévelopeurs, vu son coût moindre en comparaison avec les circuits intégrés à application spécifique.

L'algorithme CORDIC (COordinate Rotation Digital Computer) effectue la rotation d'un vecteur dans un plan à deux dimensions pour des coordonnées polaires, linéaires et hyperboliques. L'avantage de cet algorithme est qu'il permet le calcul de plusieurs fonctions élémentaires avec une implémentation matérielle relativement simple. L'algorithme CORDIC est très polyvalent, et il a été utilisé dans bon nombre d'applications, notamment le traitement numérique du signal, l'infographie 3D, les récepteurs sans fil, l'algèbre matricielle et la robotique.

Le présent ouvrage traite du développement de plusieurs différents types de processeurs CORDIC optimisés pour implémentation sur réseau prédiffusé programmable par l'utilisateur, avec un accent sur les compromis entre la surface et la performace de chaque type d'architecture. Afin de pouvoir créer rapidement ces différents processeurs, un outil capable de générer automatiquement le code source a été mis au point. Ces implémentations de l'algorithme CORDIC peuvent être utilisées dans plusieurs applications différentes, et sont particulièrement bien adaptées pour les systèmes sur une puce.

# TABLE OF CONTENTS

|   |                   |                           |                                           |   | Page |  |

|---|-------------------|---------------------------|-------------------------------------------|---|------|--|

|   | Abs               | tract .                   |                                           |   | iv   |  |

|   | Rés               | umé .                     |                                           |   | v    |  |

|   | List              | of Tab                    | oles                                      |   | xi   |  |

|   | List              | List of Figures           |                                           |   |      |  |

|   | List              | of Abb                    | previations                               |   | xiv  |  |

| 1 | Introduction      |                           |                                           |   |      |  |

|   | 1.1               | Gener                     | al Overview                               |   | 1    |  |

|   | 1.2               | Motiv                     | vation                                    |   | 2    |  |

|   | 1.3               | Objec                     | etive                                     |   | 3    |  |

|   | 1.4               | Thesis                    | s Outline                                 |   | 3    |  |

| 2 | Background Theory |                           |                                           |   |      |  |

|   | 2.1               | CORI                      | DIC Algorithm                             |   | 6    |  |

|   |                   | 2.1.1                     | Given's Transform                         |   | 6    |  |

|   |                   | 2.1.2                     | Pseudo-Rotations and Scaling Constant     |   | 6    |  |

|   |                   | 2.1.3                     | Arc Tangent Radix                         | • | ,8   |  |

|   |                   | 2.1.4                     | CORDIC Pseudo-Rotation Equations          |   | 9    |  |

|   | 2.2               | Unifie                    | d CORDIC Algorithm                        |   | 11   |  |

|   | 2.3               | 3 Algorithm Modifications |                                           |   |      |  |

|   |                   | 2.3.1                     | Hybrid Radix Sets and Rotation Prediction |   | 12   |  |

|   |                   | 2.3.2                     | Modified ATR Sets                         |   | 13   |  |

|   |                   | 2.3.3                     | Combined Successive Iterations            |   | 14   |  |

|   | •                 | 2.3.4                     | Scaling Factor Compensation               |   | 17   |  |

4.3

38

42

45

89

List of References

| Append | lix A  | Mathematical Derivations                            |

|--------|--------|-----------------------------------------------------|

| A.1    | Double | Shift Scaling Factor                                |

| A.2    | True C | Compensated CORDIC Scaling Factor                   |

| A.3    | Modifi | ed Compensated CORDIC ATR Angles and Scaling Factor |

| Append | lix B  | Error Analysis Supplement                           |

| B.1    | Angula | ar Error                                            |

# LIST OF TABLES

|     |                                                  | Page |

|-----|--------------------------------------------------|------|

| 4.1 | Compensated CORDIC Shift Sequence and Properties | 44   |

| 4.2 | Angular Error Analysis - 16 bit Inputs           | 46   |

| 7.1 | CORDIC PE Data Characteristics                   | 76   |

| 7.2 | Results for 12-bit Pipelined Architectures       | 78   |

| 7.3 | Results for 16-bit Pipelined Architectures       | 78   |

| 7.4 | Results for 24-bit Pipelined Architectures       | 79   |

| 7.5 | Results for 32-bit Pipelined Architectures       | 79   |

| 7.6 | Results for 12-bit Iterative Architectures       | 82   |

| 7.7 | Results for 16-bit Iterative Architectures       | 82   |

| 7.8 | Results for 24-bit Iterative Architectures       | 83   |

| 7.9 | Results for 32-bit Iterative Architectures       | 83   |

| B.1 | Truncation Error Analysis - Conventional CORDIC  | 99   |

| B.2 | Truncation Error Analysis - Compensated CORDIC   | 100  |

# LIST OF FIGURES

|      |                                                | Page |

|------|------------------------------------------------|------|

| 3.1  | Virtex II Logic Cell                           | . 28 |

| 3.2  | Bit-Parallel Iterative CORDIC Structure [1]    | . 33 |

| 3.3  | Unrolled Bit-Parallel CORDIC Processor [1]     | . 34 |

| 3.4  | Bit-Serial Iterative CORDIC [1]                | . 35 |

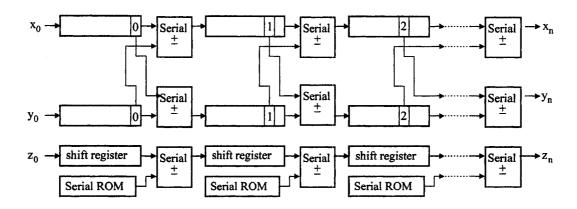

| 3.5  | Bit-Serial Pipelined CORDIC                    | . 36 |

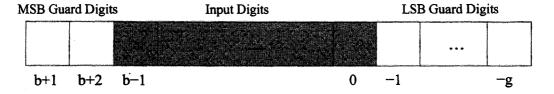

| 4.1  | x and $y$ Datapath Format                      | . 48 |

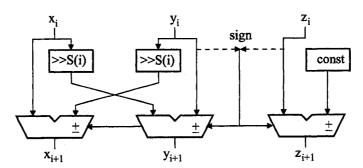

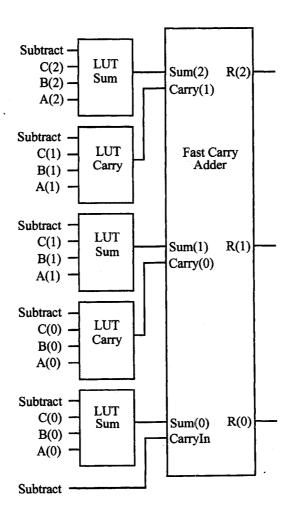

| 5.1  | Regular CORDIC Pipeline Stage                  | . 49 |

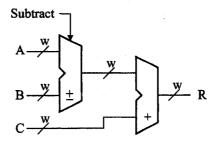

| 5.2  | 3 Operand Adder/Subtracter                     | . 50 |

| 5.3  | 3:2 Compressor and Adder                       | . 51 |

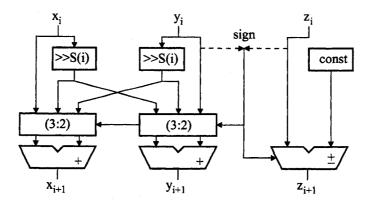

| 5.4  | Compensated Pipeline Stage                     | . 52 |

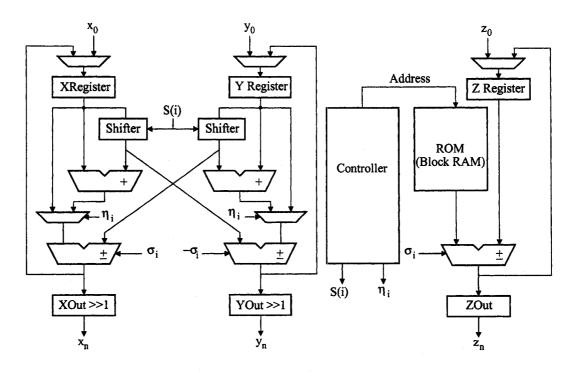

| 5.5  | Bit-Parallel Iterative Implementation          | . 53 |

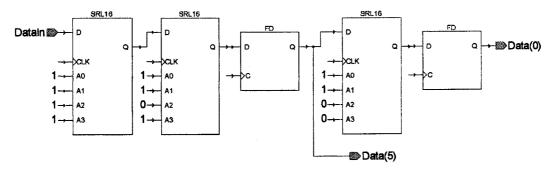

| 5.6  | 34-bit Tapped Shift Register with LSB Output   | . 54 |

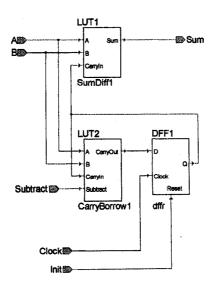

| 5.7  | Bit-Serial Add/Subtract Element                | . 55 |

| 5.8  | Bit-Serial Compensated Element                 | . 56 |

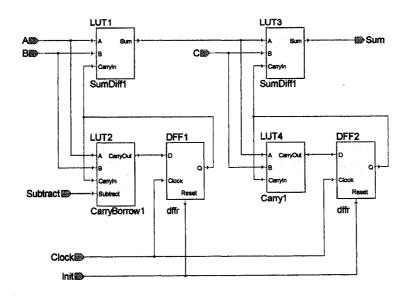

| 5.9  | Pipe Section - $x$ and $y$ Data path           | . 57 |

| 5.10 | Pipe Section - z Data path                     | . 57 |

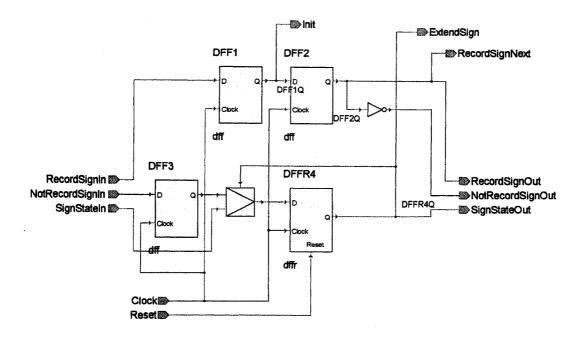

| 5.11 | External Control Pipe Section                  | . 58 |

| 5.12 | External Control Timing (8 Bits, 4 Iterations) | . 58 |

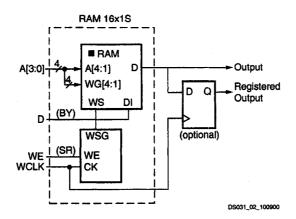

| 5.13 | Virtex-II CLB RAM                              | . 60 |

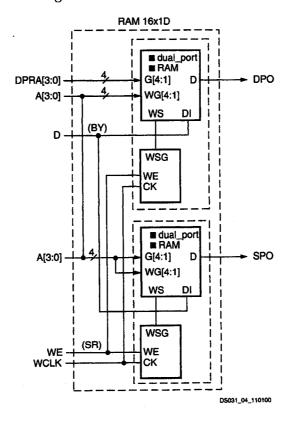

| 5.14 | Virtex-II Dual Port RAM                        | . 60 |

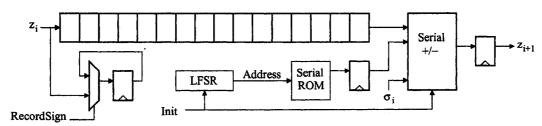

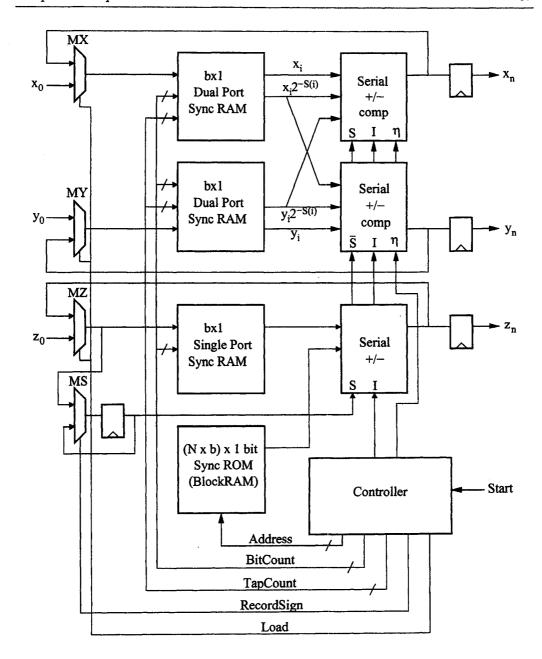

| 5.15 | Bit-Serial Iterative Architecture              | . 62 |

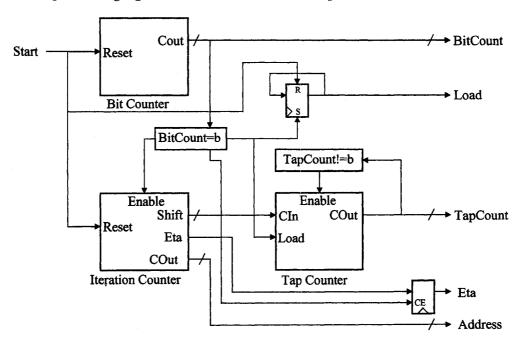

| 5.16 | Bit-Serial Iterative Controller                | . 63 |

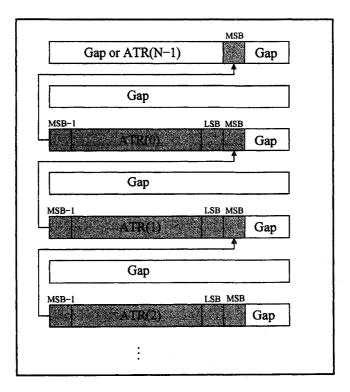

| 5.17 | ATR ROM Memory Layout                          | . 64 |

# LIST OF ABBREVIATIONS

ASIC - Application Specific Integrated Circuit

CLB - Configurable Logic Block

CORDIC - COordinate Rotation Digital Computer

DCM - Digital Clock Manager

DSP - Digital Signal Processing

FG - Function Generator

FPGA - Field Programmable Gate Array

I/O - Input Output

LFSR - Linear Feedback Shift Register

LSB - Least Significant Bit

LUT - Look Up Table

MSB - Most Significant Bit

NRE - Non-Recurrent Engineering

PE - Processing Element

RAM - Random Access Memory

ROM - Read Only Memory

RNS - Redundant Number System

SoC - System on Chip

VHDL - VHSIC Hardware Description Language

VHSIC - Very High Speed Integrated Circuit

## CHAPTER 1: INTRODUCTION

#### 1.1 General Overview

The CORDIC (COrdinate Rotation Digital Computer) is an extremely versatile algorithm for numerical computations. It is essentially a simple hardware implementation of the Given's Transform for vector rotation in the 2D plane, and was first presented in 1959 by J.E. Volder [2]. It was later extended by Walther [3] who proposed a unified CORDIC algorithm capable of performing vector rotations in the circular, hyperbolic and linear coordinate systems. By using a CORDIC rotator, it is possible to calculate various trigonometric and hyperbolic functions, natural logarithms, natural exponential, square root, multiplication, polar to rectangular and rectangular to polar conversion. As such, the CORDIC algorithm can be used in any application which requires such computations, such as Digital Signal Processing, 3D Computer Graphics, Wireless Receivers, Matrix Algebra and Robotics, to name only a few. The floating point version of the CORDIC algorithm is used when large dynamic ranges are required, particularly in 3D Computer Graphics, Numerical Computing, Medical Research and Robotics. Some of the more notable historical applications that have made use of the CORDIC algorithm include airborne navigation (for which the algorithm was originally intended), the Hewlett Packard HP-35 scientific calculator and the Intel 8087 math co-processor.

Modern applications, such as DSP and 3D computer graphics, have ever increasing processing requirements due to the need for higher resolution and real-time applications. In order to provide the required computing power for such applications, there has been a shift from software to specialized hardware. The need for smaller devices across a wide range of applications has also been a major driving force in the proliferation of hardware solutions. An important trend resulting from this and made possible by advances in VLSI technology has been the System on Chip (SoC)

approach to hardware design. SoC are complex integrated circuits that include almost all system components and interfacing hardware on a single chip or chip set.

#### 1.2 Motivation

Traditionally, SoC designs were implemented on custom Application Specific Integrated Circuits (ASICs). ASICs require an elaborate development process, have substantial non-recurrent engineering (NRE) costs and may present a high degree of risk. They are simply not a viable option for prototyping and small to medium volume production. An alternative to the high cost ASIC are the Field Programmable Gate Arrays (FPGAs). Advances in FPGA technology now provides the hardware designer with large devices that can run at speeds of several hundred megahertz. In addition to the ever increasing number of logic elements and wiring resources, manufacturers now provide special-purpose resources such as Block RAM, multipliers, analog to digital and digital to analog converters and even entire "hard" microprocessors in a single device. This has made the FPGA a solid platform for SoC applications, along with its much simpler design flow, low NRE costs and very low degree of risk.

Designing optimized logic for implementation on an FPGA is quite different than designing digital circuits at the transistor level or using a standard cell library. The logic elements available on the FPGA impose certain limitations. In order to squeeze out maximum performance or use the least amount of space possible, the designer must find clever ways of using the available logic elements to his advantage.

Since the CORDIC algorithm is used in a wide range of different SoC applications, it is one of the most important algorithms to optimize for implementation on an FPGA. This optimization can be for area, speed, power dissipation or a combination of these. Additionally, there are many applications that require a number of different CORDIC processing elements. Examples of such applications include the Discrete Cosine Transform [4], the Fast Fourier Transform [5] and matrix transformations [6].

# 1.3 Objective

The aim of this thesis is to develop several different types of CORDIC processing elements specifically optimized for FPGA implementation, and to study the area-performance tradeoffs of each. These different processing elements can then be used in a variety of applications. Particular attention will be devoted to SoC applications, where relatively small area utilization is required.

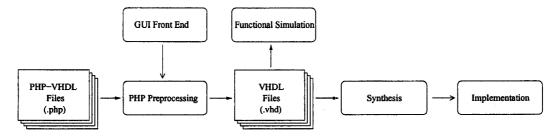

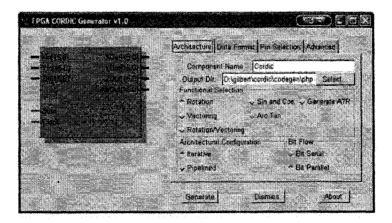

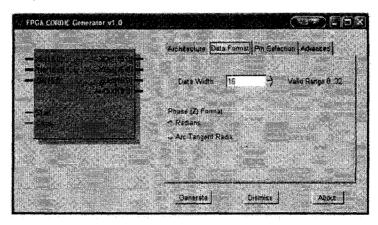

In order to achieve this aim, a number of different objectives must be met. The first is to conduct an extensive survey of the state of the art in terms of the CORDIC algorithm. There has been an astounding number of different modifications that have been proposed for the algorithm in an attempt to increase its efficiency. However, not all these can be successfully applied to FPGAs, and the architectural details of the FPGA must be carefully considered when determining what CORDIC variants are suitable for implementation. The chosen algorithm will be adapted to different types of architectural styles, taking into consideration precision requirements. Functional simulation will need to be carried out on these different architectures in order to ensure correctness of the implementation. In order to provide usable components for inclusion into larger designs, an automatic code generation tool will be developed. This tool will be capable of generating processing elements according to user specified parameters. Xilinx, the leading FPGA manufacturing company, already provides such a tool called Core Generator, which includes, among other types of modules, a CORDIC module. The generated CORDIC processing elements from the custom code generation tool will be benchmarked against those produced by the Xilinx tool.

#### 1.4 Thesis Outline

This thesis is broken down into eight chapters, including this introductory chapter. Chapter 2 presents the original CORDIC algorithm proposed by Volder and describes some of the more notable modifications presented by various researchers.

Chapter 3 examines the low level details of the programmable logic platform chosen for this thesis, the Xilinx Virtex-II. This chapter will also examine the four broad architectural styles that have been deemed the most useful for implementation of the CORDIC algorithm on an FPGA. Chapter 4 includes a comparison of the two most promising alternative CORDIC algorithms and selection of the best algorithm for implementation on the target platform. This chapter also includes error analysis and details on the internal data path format. Chapter 5 contains the hardware implementation details of the chosen CORDIC algorithm for all four architectural styles. Chapter 6 presents a novel technique used for automatic VHDL code generation and describes the tool used to generate the different CORDIC processing elements. Chapter 7 provides characterization data and benchmarks for the different CORDIC PE architectures. Finally, chapter 8 contains the conclusions and recommendations for future work resulting from this thesis.

# CHAPTER 2: BACKGROUND THEORY

The term COordinate Rotation Digital Computer (CORDIC) was first coined by J. E. Volder in 1959 in his landmark paper The CORDIC Trigonometric Computing Technique [2]. He initially developed the CORDIC special purpose digital computer for real-time computation in support of airborne navigation. The CORDIC computer described by Volder essentially rotates a vector  $\vec{v}$  in the 2D plane in incremental steps, and it has two different modes of operation: rotation and vectoring.

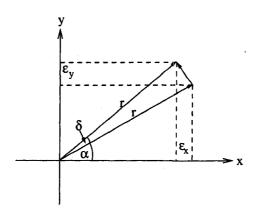

In rotation mode, a vector with the specified x and y end coordinates is rotated about the origin by an angle  $\alpha$  as specified by the Given's Transform equation:

$$x' = x\cos\alpha - y\sin\alpha \tag{2.1}$$

$$y' = y\cos\alpha + x\sin\alpha \tag{2.2}$$

In *vectoring* mode, the inputs are the vector end coordinates and the results are the vector magnitude and angle argument:

$$\|\vec{v}\| = \sqrt{x^2 + y^2} \tag{2.3}$$

$$\alpha = \arctan \frac{y}{x} \tag{2.4}$$

The basic computing technique in both of these modes is a step-by-step sequence of incremental rotations that will either be equivalent to the desired overall rotation (*rotation* mode) or result in a final angle residual of zero (*vectoring* mode).

# 2.1 CORDIC Algorithm

# 2.1.1 Given's Transform

The CORDIC algorithm is elegantly demonstrated by making use of the Given's transform which performs 2D vector rotations in the Cartesian plane:

$$x' = x\cos\alpha - y\sin\alpha \tag{2.5}$$

$$y' = y\cos\alpha + x\sin\alpha \tag{2.6}$$

Equations 2.5 and 2.6 gives the relationship for converting the initial (x, y) coordinates into the new (x', y') coordinates after rotating the vector by an angle of  $\alpha$  in the cartesian plane. The first key concept in the CORDIC algorithm is that a rotation by an angle  $\alpha$  in the cartesian plane can also be accomplished by successive rotations of smaller angles  $\alpha_i$  such that:

$$\sum_{i=0}^{N-1} \alpha_i = \alpha \tag{2.7}$$

The equations defining these smaller iterations are thus:

$$x_{i+1} = x_i \cos \alpha_i - y_i \sin \alpha_i \tag{2.8}$$

$$y_{i+1} = y_i \cos \alpha_i + x_i \sin \alpha_i \tag{2.9}$$

## 2.1.2 Pseudo-Rotations and Scaling Constant

In an attempt to further simplify the basic iteration equations, it is possible to take out the  $\cos \alpha_i$  factor out of each iteration equation. Consider that cosine is an even function, that is  $\cos(\alpha) = \cos(-\alpha)$ . Thus, for two consecutive rotations, we have:

$$x_{i+1} = \cos \alpha_i (x_i - y_i \tan \alpha_i) \tag{2.10}$$

$$y_{i+1} = \cos \alpha_i (y_i + x_i \tan \alpha_i) \tag{2.11}$$

$$x_{i+2} = \cos \alpha_{i+1} (x_{i+1} - y_{i+1} \tan \alpha_{i+1}) \tag{2.12}$$

$$y_{i+2} = \cos \alpha_{i+1} (y_{i+1} + x_{i+1} \tan \alpha_{i+1}) \tag{2.13}$$

Considering only the x coordinate, we have:

$$x_{i+2} = \cos \alpha_{i+1} \left[\cos \alpha_i (x_i - y_i \tan \alpha_i) - \cos \alpha_i (y_i + x_i \tan \alpha_i) \tan \alpha_{i+1}\right]$$

(2.14)

$$x_{i+2} = \cos \alpha_i \cos \alpha_{i+1} [(x_i - y_i \tan \alpha_i) - (y_i + x_i \tan \alpha_i) \tan \alpha_{i+1}]$$

(2.15)

Hence, the  $\cos \alpha_i$  factors can be taken out from each iteration, and can be taken care of separately. What is left is a pair of new iteration equations which are called *pseudo-rotations*:

$$x_{i+1} = x_i - y_i \tan \alpha_i \tag{2.16}$$

$$y_{i+1} = y_i + x_i \tan \alpha_i \tag{2.17}$$

Considering the relationship between *pseudo-rotations* and pure rotations as per the Given's Transform, we have:

$$x_i - y_i \tan \alpha_i = \cos^{-1} \alpha_i (x_i \cos \alpha_i - y_i \sin \alpha_i)$$

(2.18)

$$y_i + x_i \tan \alpha_i = \cos^{-1} \alpha_i (y_i \cos \alpha_i + x_i \sin \alpha_i)$$

(2.19)

Equations 2.18 and 2.19 clearly indicate that pseudo-rotations will induce growth in the vector being rotated. The magnitude of this growth is determined by the scaling factor K. For N pseudo-rotations, the final coordinates are given by:

$$x' = [x_{N-1}\cos\alpha_{N-1} - y_{N-1}\sin\alpha_{N-1}] \tag{2.20}$$

$$y' = [y_{N-1}\cos\alpha_{N-1} + x_{N-1}\sin\alpha_{N-1}] \tag{2.21}$$

$$x' = K^{-1} \left[ x_{N-1} - y_{N-1} \tan \alpha_{N-1} \right] \tag{2.22}$$

$$y' = K^{-1} \left[ y_{N-1} + x_{N-1} \tan \alpha_{N-1} \right]$$

(2.23)

Where the scaling factor K is defined as:

$$K = \prod_{i=0}^{N-1} \cos^{-1} \alpha_i \tag{2.24}$$

# 2.1.3 Arc Tangent Radix

Equations 2.16 and 2.17 provide for efficient computation, since they are composed of only one addition and one multiplication. By choosing the values of  $\tan \alpha_i$  so that they are fractional powers of two, multiplication by  $\tan \alpha_i$  is performed using simple right shift operations. Also note that for the special case of  $\alpha = \pi/2$  rad:

$$x' = -y \tag{2.25}$$

$$y' = +x \tag{2.26}$$

Following is a partial table of tangent values that are fractional powers of two:

| Tangent                  | Corresponding Angle                             |  |  |

|--------------------------|-------------------------------------------------|--|--|

|                          | ·                                               |  |  |

| $\tan \alpha_s = \infty$ | $\alpha_s = \pi/2  \mathrm{rad}$ (special case) |  |  |

| $\tan \alpha_0 = 1$      | $\alpha_0=0.785398\mathrm{rad}$                 |  |  |

| $\tan \alpha_1 = 2^{-1}$ | $\alpha_1=0.463648\mathrm{rad}$                 |  |  |

| $\tan\alpha_2=2^{-2}$    | $\alpha_2=0.244979\mathrm{rad}$                 |  |  |

| $\tan\alpha_3=2^{-3}$    | $\alpha_3=0.124355\mathrm{rad}$                 |  |  |

| $\tan \alpha_4 = 2^{-4}$ | $\alpha_4=0.062419\mathrm{rad}$                 |  |  |

| $\tan\alpha_5=2^{-5}$    | $\alpha_5=0.031240\mathrm{rad}$                 |  |  |

| $\tan\alpha_6=2^{-6}$    | $\alpha_6=0.015624\mathrm{rad}$                 |  |  |

| $\tan \alpha_7 = 2^{-7}$ | $\alpha_7=0.007812\mathrm{rad}$                 |  |  |

These angles can be combined together in a sequence to form a special radix representation for a given angle  $\alpha$  as follows:

$$\alpha = \sum_{i=0}^{N-1} \sigma_i \alpha_i \tag{2.27}$$

where  $\alpha_i$  represents the Arc Tangent Radix (ATR) constants and  $\sigma_i$  are the ATR digits. For reasons of computational efficiency, the ATR digits are restricted to  $\{-1, +1\}$ .

For example, an angle of  $\frac{5\pi}{180} \approx 0.087266$  rad would be obtained in the following manner:

$$+\pi/2 - \arctan(2^0) - \arctan(2^{-1}) - \arctan(2^{-2}) + \arctan(2^{-3})$$

$-\arctan(2^{-4}) - \arctan(2^{-5}) - \arctan(2^{-6}) - \arctan(2^{-7}) \approx 0.084032 \,\mathrm{rad}$

It's ATR digit vector is thus  $\sigma = (+1, -1, -1, -1, -1, -1, -1, -1, -1, -1)$ , and forms an alternative representation of the angle. These digits indicate whether the next rotation will be positive or negative. Also note that the precision of the ATR representation obtained for an angle is dependent on the smallest angle present in the ATR constants set.

From the preceding discussion, it can be seen that the ATR constants are also used in order to calculate the scaling factor K. By keeping  $\sigma_i \in \{-1, 1\}$ , a constant scaling factor is ensured since  $\cos(-\alpha_i) = \cos \alpha_i$ . The expression for  $\cos \alpha_i$  is derived as follows:

$$\tan \alpha_i = \frac{y}{x} = \frac{1}{2^i}$$

$$\vec{v} = \sqrt{y^2 + x^2} = \sqrt{1 + 2^{2i}}$$

$$\cos \alpha_i = \frac{x}{\vec{v}} = \frac{2^i}{\sqrt{1 + 2^{2i}}} = \frac{1}{\sqrt{1 + 2^{-2i}}}$$

And the scaling factor becomes:

$$K = \prod_{i=0}^{N-1} \sqrt{1 + 2^{-2i}} \tag{2.28}$$

For an infinite number of iterations, the inverse scaling factor would evaluate to the following series:

$$K^{-1} = \prod_{i=0}^{\infty} \frac{1}{\sqrt{1+2^{-2i}}} = 0.607253 \tag{2.29}$$

# 2.1.4 CORDIC Pseudo-Rotation Equations

When implementing the CORDIC algorithm, an angle accumulator is used in order to make a decision on the direction of the next rotation.

In rotation mode, the target angle value  $\alpha$  is first loaded in the accumulator. At each step, a decision will be made in order to diminish the magnitude of the residual angle in the register. If the residual angle is positive, the next ATR constant needs to be subtracted from the accumulator; otherwise, the next ATR constant has to be added to the accumulator. At the end of all the iterations, only a very small residual angle should be left in the accumulator.

In *vectoring* mode, the decision will be made in order to diminish the magnitude of the current y component. At the end of all the pseudo-rotations, the residual y component has to be as close to zero as possible. In this way, the last calculated x value will contain the magnitude of the vector, and the angle register will contain the total rotation angle  $\alpha$ . At each step, if the residual y value is positive, the next ATR constant has to be added to the accumulator; otherwise, the next ATR constant gets subtracted from the angle accumulator.

From these statements, the CORDIC pseudo-rotation equations for *rotation* mode are as follows:

$$x_{i+1} = x_i - \sigma_i y_i 2^{-i} (2.30)$$

$$y_{i+1} = y_i + \sigma_i x_i 2^{-i} (2.31)$$

$$z_{i+1} = z_i - \sigma_i \alpha_i \tag{2.32}$$

$$\sigma_{i} = \begin{cases} -1 & \text{if } z_{i} < 0 \\ +1 & \text{otherwise} \end{cases}$$

(2.33)

The equations for *vectoring* mode are exactly the same. This is obvious, since the rotation operation is the same. The only difference is the condition for the rotation direction,  $\sigma_i$ , which now becomes:

$$\sigma_i = \begin{cases} +1 & \text{if } y_i < 0 \\ -1 & \text{otherwise} \end{cases}$$

(2.34)

#### 2.2 Unified CORDIC Algorithm

By slightly modifying the pseudo-rotation equations, Walther [3] was able to present a unified CORDIC algorithm capable of performing rotations in the linear and hyperbolic coordinate systems in addition to the circular rotations first presented by Volder. The unified CORDIC pseudo-rotation equations are given by:

$$x_{i+1} = x_i - m\sigma_i 2^{-S(m,i)} y_i (2.35)$$

$$y_{i+1} = y_i + \sigma_i 2^{-S(m,i)} x_i \tag{2.36}$$

$$z_{i+1} = z_i - \sigma_i \alpha_{m,i} \tag{2.37}$$

where m=1 for circular, m=0 for linear and m=-1 for hyperbolic coordinate systems. The direction of rotation for both rotation and vectoring modes are still  $\sigma_i = sign(z_i)$  and  $\sigma_i = -sign(y_i)$  respectively. The S(m,i) variables indicate the amount of shift for each iteration. Throughout this text, if the m variable is missing, it is assumed that m=1, or S(i)=S(1,i), corresponding to the circular coordinate system. In the circular and linear coordinate systems, the shift sequences are given by S(1,i)=S(0,i)=(0,1,2,3,...). In order to preserve convergence, the hyperbolic coordinate system requires that certain elements in the shift sequence be repeated. Convergence in the CORDIC algorithm will be discussed in further sections. Thus, the shift sequence for the hyperbolic coordinate system is S(-1,i)=(1,2,3,4,4,5,...,12,13,13,14,...) where the repeated elements are given by  $\{3k+1\}$ ,  $k \in N$ . The scaling factor for the hyperbolic and circular coordinate systems is now given by:

$$K_{m,i} = \prod_{i=0}^{N-1} \sqrt{1 + m\sigma_i^2 2^{-2S(m,i)}}$$

(2.38)

Note that scaling is not applicable to the linear coordinate system. Also, the angle basis for the unified CORDIC now becomes:

$$\alpha_{m,i} = \frac{1}{\sqrt{m}} \arctan\left(\sqrt{m} 2^{-S(m,i)}\right) \tag{2.39}$$

#### 2.3 Algorithm Modifications

Following the initial work on the CORDIC algorithm by Volder and Walther, there has been a tremendous amount of work aimed at improving the basic CORDIC algorithm. The bulk of this work has been in devising "short-cut" methods in order to speed up the algorithm. The most notable ideas are presented in this section and are grouped into broad categories.

# 2.3.1 Hybrid Radix Sets and Rotation Prediction

The main bottleneck of the CORDIC algorithm lies in the fact that the direction of rotation for a particular iteration depends on the results of the previous iteration. If the Arc Tangent Radix representation of the angle is known in advance, then there is no dependency on the previous iterations and there is no need for the z data path (in rotation mode). However, the input angle is usually encoded in conventional two's complement representation. There have been numerous publications which discuss the process of deriving the ATR representation directly from the two's complement representation of the angle. These are usually based on the Hybrid Radix Set discussed in [7].

Hybrid radix sets rely on the following relationship:

$$\lim_{k \to \infty} \frac{\tan 2^{-k}}{2^{-k}} = 1 \tag{2.40}$$

As k increases, the difference between the circular ATR angles and the radix-2 shift coefficients becomes more and more negligeable. However, for small values of k, this difference is quite large. The solution proposed in [7] is to use the circular ATR angle rotations for the first n iterations, and use the linear coefficients for the remainder of the iterations. In fact, it is shown in [7] that  $n = \left\lceil \frac{N - \log_2 3}{N} \right\rceil$ . This Mixed-Hybrid Radix Set is of the form:

$$\{ \underbrace{\arctan \infty, \arctan 1, \arctan 2^{-1}, \ldots, \arctan 2^{-n+1}}_{\text{least significant part}} \}$$

When such an angle quantization method is used, iterations 0 to iteration (n-1) are performed as in the original CORDIC. At the end of these first iterations, there will be an angle residual left in the angle accumulator. The value of the residual angle is the radix-2 representation (approximation) of the remaining angle rotation in the linear coordinate system. In the case of a positive residual angle, a 1 indicates a positive rotation and a 0 indicates a non-rotation. A similar approach can be used for negative residual angles. Introducing non-rotations will lead to a non-constant scaling factor, since for a rotation by  $\alpha_i = 0$ , we have  $\cos \alpha_i = \cos(\arctan 0) = 1$ . The only way to keep the scaling factor constant is to perform either a positive or negative rotation at every iteration, since  $\cos(\arctan(-2^{-i})) = \cos(\arctan 2^{-i})$ . The authors in [7] also note that the computation of  $\alpha_H$ , the most significant part of  $\alpha$  might impact  $\alpha_L$ , the least significant part of  $\alpha$ . Hence, there must be a separation of the rotation prediction for  $\alpha_H$  and  $\alpha_L$ .

The problem then becomes the prediction of the first n terms which are not directly available from the two's complement representation of the input angle. One way of accomplishing this is by compressing the  $\alpha_H$  rotations into a single rotation that is implemented by the use of a ROM as discussed in [7]. Others have developed combinational means of generating the  $\alpha_H$  ATR digits [8] [9]. Usage of the Booth encoding algorithm has also been used in order to recode angles [10] [11].

#### 2.3.2 Modified ATR Sets

The term Angle Set designates the elementary angles which form a radix representation of an angle. The Angle Set is an important factor when examining the CORDIC algorithm. One obvious impact in the choice of an Angle Set is in the accuracy of the results. The Angle Set also has a direct influence on the scaling factor

and on rotation direction determination. An excellent generalization concerning Angle Set Selection can be found in [12]. In this work, the authors discuss the concept of Angle Quantization, which is defined as the process of decomposing an arbitrary angle  $\theta$  in terms of a set of sub-angles  $\theta_i$ . In Volder's original work [2], the term Arc Tangent Radix (ATR) was used in order to stress the fact that these sub-angles were expressed as  $\alpha_i = \arctan(2^{-i})$ . However, the terminology found in [12] will be used in order to demonstrate this concept.

The Elementary Angle Set (EAS) is defined as:

$$S_1 = \left\{\arctan(\sigma 2^{-k}) : \sigma \in \{-1, 0, 1\}, k \in \{0, 1, \dots, N - 1\}\right\}$$

(2.41)

From this definition, it can be seen that Volder's ATR representation is a subset of the EAS where  $\sigma \in \{-1, 1\}$ . The ATR representation ensures that for a fixed number of iterations, the scaling factor will remain constant. However, the definition of the EAS allows for the possibility that a rotation might not be executed during a particular iteration (i.e. when  $\sigma = 0$ ). In this case, the scaling factor does not remain constant.

The Extended Elementary Angle Set (EEAS) is defined as:

$$S_2 = \left\{ \arctan(\sigma_0 2^{-k_0} + \sigma_1 2^{-k_1}) : \sigma_0, \sigma_1 \in \{-1, 0, 1\}, k_0, k_1 \in \{0, 1, \dots, N - 1\} \right\}$$

$$(2.42)$$

The EEAS allows for more flexibility in the choice of angles that make up the set. This flexibility can actually be used in order to "steer" the scaling factor to a Signed Power of Two (SPT), which would eliminate the need for a costly post-scaling multiplier.

#### 2.3.3 Combined Successive Iterations

In order to solve different types of bottlenecks with the CORDIC iterations, researchers have combined successive iterations. The way that successive iterations are combined depends on the problem that is being addressed. Some of these solutions are concerned with angle convergence, others are concerned with scaling factor and others still try to increase the parallelism of the CORDIC process.

There have been several attempts made at combining two successive CORDIC iterations into a single iteration. *Double Rotation CORDIC* is derived as follows:

$$x_{i+1} = x_i - y_i \sigma_i 2^{-i} \tag{2.43}$$

$$y_{i+1} = y_i + x_i \sigma_i 2^{-i} \tag{2.44}$$

$$x_{i+2} = x_{i+1} - y_{i+1}\sigma_{i+1}2^{-i} (2.45)$$

$$x_{i+2} = (x_i - y_i \sigma_i 2^{-i}) - (y_i + x_i \sigma_i 2^{-i}) \sigma_{i+1} 2^{-i+1}$$

(2.46)

$$x_{i+2} = x_i(1 - \sigma_i \sigma_{i+1} 2^{-i} 2^{-i+1}) + y_i(\sigma_i 2^{-i} + \sigma_{i+1} 2^{-i+1})$$

(2.47)

$$y_{i+2} = y_i(1 - \sigma_i \sigma_{i+1} 2^{-i} 2^{-i+1}) - x_i(\sigma_i 2^{-i} + \sigma_{i+1} 2^{-i+1})$$

(2.48)

In [13], the combination of two successive iterations provides for a new angle recoding scheme. The recoding scheme uses a ROM based approach in order to encode the required rotation directions for each angle. In this manner, the algorithm has a non-constant scaling factor, and relies on a fast variable scale factor decomposition and compensation algorithm.

Another well known paper that uses this approach is found in [14]. In this paper, double rotations are introduced in order to correct the scale factor issues associated with the Redundant CORDIC, and it uses the redundant binary number representation with the digit set of  $\{\overline{1},0,1\}$ . The Double Rotation CORDIC performs three types of rotations: negative, positive and non-rotation. These three types of rotations are performed with the help of two consecutive sub-rotations (hence the term Double Rotation). The smaller sub rotation angles are chosen such that their arctangent value are half those of regular CORDIC, that is  $\arctan \frac{2^{-i}}{2} = \arctan 2^{-i-1}$ . Interestingly enough, all possible rotation angles performed in Regular CORDIC will also be used in this algorithm; however, each rotation will be applied twice. The double rotations are derived in a slightly different way:

$$x_{i+1} = x_i - y_i \sigma_i 2^{-i-1} (2.49)$$

$$y_{i+1} = y_i + x_i \sigma_i 2^{-i-1} (2.50)$$

Considering only the x data path, we have:

$$x_{i+2} = x_{i+1} - y_{i+1}\sigma_{i+1}2^{-i-1} (2.51)$$

$$x_{i+2} = \left[x_i - y_i \sigma_i 2^{-i-1}\right] - \left[y_i + x_i \sigma_i 2^{-i-1}\right] \sigma_{i+1} 2^{-i-1}$$

(2.52)

$$x_{i+2} = x_i - 2^{-1} \left[ \sigma_i + \sigma_{i+1} \right] y_i 2^{-i} - \left[ \sigma_i \cdot \sigma_{i+1} \right] x_i 2^{-2i-2}$$

(2.53)

Setting  $q_i = 2^{-1} \left[ \sigma_i + \sigma_{i+1} \right]$  and  $p_i = \left[ \sigma_i \cdot \sigma_{i+1} \right]$  we have

$$x_{i+2} = x_i - q_i y_i 2^{-i} - p_i x_i 2^{-2i-2}$$

(2.54)

The positive, negative and non rotations are thus defined as follows:

negative rotations :  $\sigma_i = \overline{1}, \sigma_{i+1} = \overline{1} \Rightarrow q_i = \overline{1}, p_i = 1$

nonrotations:  $\sigma_i = \overline{1}, \sigma_{i+1} = 1 \Rightarrow q_i = 0, p_i = \overline{1}$

positive rotations:  $\sigma_i = 1, \sigma_{i+1} = 1 \Rightarrow q_i = 1, p_i = 1$

Since there is no need for an i+1 iteration, i and i+2 effectively become two successive iterations. Note also that the decision for the direction of the rotation  $(q_i$  and  $p_i)$  are based on the three most significant digits of  $z_j$ . Thus, the pseudo-rotation and decision equations can be written as follows:

$$x_{j+1} = x_j - q_j y_j 2^{-j} - p_j x_j 2^{-2j-2}$$

(2.55)

$$y_{j+1} = y_j + q_j x_j 2^{-j} - p_j y_j 2^{-2j-2}$$

(2.56)

$$z_{j+1} = z_j - q_j 2 \arctan 2^{-i-1} (2.57)$$

$$(q_{j}, p_{j}) = \begin{cases} (\overline{1}, 1) & \text{if } [z_{j}^{j-1} z_{j}^{j} z_{j}^{j+1}] < 0, \\ (0, \overline{1}) & \text{if } [z_{j}^{j-1} z_{j}^{j} z_{j}^{j+1}] = 0, \\ (1, 1) & \text{if } [z_{j}^{j-1} z_{j}^{j} z_{j}^{j+1}] > 0. \end{cases}$$

$$(2.58)$$

As previously mentioned, the main limiting factor of the CORDIC algorithm is that it is iterative in nature, i.e. the value of  $x_{i+1}$  and  $y_{i+1}$  are a function of both

$x_i$  and  $y_i$ . By successive substitutions of  $x_i$  and  $y_i$  in the basic CORDIC equations, it is possible to derive an expression for the final values  $x_N$  and  $y_N$  that is only dependent on  $x_0$  and  $y_0$  [15]. This type of algorithm is called the *Flat CORDIC*, and the resulting expressions become quite simple to implement at the hardware level. However, the drawback of Flat CORDIC is that the ATR representation of the angle must be available before processing; this is accomplished with the use of a specialized circuit called the *signed digit generator* in [15], and is based on rotation prediction as described in section 2.3.1.

In the derivation of the Merged CORDIC algorithm [16], matrix operations are used in order to combine successive iterations. The idea behind merging the iterations is to rearrange their sequence in such a way that the *i*th iteration is next to the (n-i+1) iteration. The resulting iteration equations of the merged CORDIC thus become:

$$x_{i+1} = x_i - (\sigma_i 2^{-i} + \sigma_{n-i+1} 2^{-n+i-1}) y_i$$

(2.59)

$$y_{i+1} = y_i + (\sigma_i 2^{-i} + \sigma_{n-i+1} 2^{-n+i-1}) x_i$$

(2.60)

$$z_{i+1} = z_i - \sigma_i \alpha_i - \sigma_{n-i+1} \alpha_{n-i+1}$$

(2.61)

With merged CORDIC there are considerable hardware savings since *n*-bit shifters are not required; only  $\frac{n}{2}$  -bit shifters are needed.

# 2.3.4 Scaling Factor Compensation

As discussed earlier, the pseudo-rotations will induce magnitude growth in the rotated vector. In order to obtain unscaled values, the final x and y values must be multiplied by the inverse scaling factor given by:

$$\frac{1}{K} = \prod_{i=0}^{N-1} \frac{1}{\sqrt{1+2^{-2i}}} \tag{2.62}$$

The most straightforward method of compensation is to multiply the final x and y values by the inverse scaling factor (post-scaling). It is also possible to perform the multiplication prior to the CORDIC iterations (pre-scaling). Multiplier recoding into Canonical Signed Digit can be used in order to simplify the multiplication.

Another method of performing compensation is to introduce *normalization* steps in between CORDIC iterations as presented in [17]. The scaling factor can be expressed as:

$$\frac{1}{K_m(n)} = \prod_{i=0}^{N-1} (1 - m\gamma_{m,i} 2^{-S(m,i)})$$

(2.63)

where  $\gamma_{m,i} \in \{0,1\}$ . Finally, the normalization steps are:

$$x_{i+1,norm} = x_{i+1} - mx_{i+1}\gamma_{m,i}2^{-S(m,i)}$$

(2.64)

$$y_{i+1,norm} = y_{i+1} - my_{i+1}\gamma_{m,i}2^{-S(m,i)}$$

(2.65)

As mentioned in 2.3.2, the *double shift* iterations of the EEAS angle set can be used in order to steer the inverse scaling to a simple sum of signed powers of two. The generalized equation of the unified CORDIC for double shift is given by:

$$x_{i+1} = x_i - m\sigma_i y_i 2^{-S(m,i)} - m\sigma_i \eta_{m,i} y_i 2^{-S'(m,i)}$$

(2.66)

$$y_{i+1} = y_i + m\sigma_i x_i 2^{-S(m,i)} + m\sigma_i \eta_{m,i} x_i 2^{-S'(m,i)}$$

(2.67)

$$\alpha_i = \frac{1}{\sqrt{m}} \arctan\left[\sqrt{m} \left(2^{-S(m,i)} + \eta_{m,i} 2^{-S'(m,i)}\right)\right]$$

(2.68)

where  $\eta_{m,i} \in \{-1,0,1\}$  and S'(m,i) is a second shift factor.

Another variation that is quite similar to the double shift CORDIC is the compensated CORDIC presented in [5]. The iteration equations for the compensated CORDIC are given by:

$$x_{i+1} = x_i - m\sigma_i y_i 2^{-S(m,i)} + \eta_{m,i} x_i 2^{-S(m,i)}$$

(2.69)

$$y_{i+1} = y_i + m\sigma_i x_i 2^{-S(m,i)} + \eta_{m,i} y_i 2^{-S(m,i)}$$

(2.70)

$$\alpha_i = \frac{1}{\sqrt{m}} \arctan\left[\frac{\sqrt{m}}{2^{S(m,i)} + \eta_{m,i}}\right]$$

(2.71)

# 2.3.5 Floating Point CORDIC

The shift and add nature of the CORDIC algorithm makes use of the fixed point format. Performance degradation would occur if these operations were to be carried out in Floating Point format, which requires more overhead.

In most cases, Floating Point implementations will convert the Floating Point input to a Fixed Point internal representations, and reconvert this internal representation to Floating Point at the output. In order to do so, a working exponent must first be determined, which is the largest of the two exponents. The mantissas of both inputs have to be aligned in order to perform the CORDIC iterations. Examples of usage of block floating point can be found in [18] [19] [20]. Another point to consider in the use of the floating point representation is that in certain applications, a fixed point representation might be all that is needed [20].

One recent paper discusses the use of the Floating Point Format for internal calculations in support of the Singular Value Decomposition Problem [21]. The authors state that the parallelism of the systolic array architecture reduces the penalty from the overhead of floating point normalization in each pipeline stage.

#### 2.3.6 Alternative Number Representation System

In attempting to improve the CORDIC algorithm, Redundant Number Systems have been used in order to speed up the arithmetic operation of addition in each iteration. The inherent difficulty in the use of such a number representation is the determination of the next direction for rotation, since the sign of a binary number can no longer be determined by simply examining the MSB. Usually, the sign of an RNS number can only be determined by starting from the MSB, and examining each digit in sequence until a non-zero digit is encountered. As discussed in [14], it is possible to examine only a limited number of bits which form a window, as all bits to the left of this window are guaranteed to be zero in the CORDIC process. Others have proposed the Branching and Double Step Branching CORDIC algorithm [22]

[23]. The Branching CORDIC requires two CORDIC processors which perform the iterations in parallel. When the sign of the next rotation can be determined from the bits within the *window*, the two processors execute the same rotation. When the direction cannot be determined, they take different rotation directions; in this way, one of the two processors is guaranteed to converge. When the next branching decision is triggered by one of the two processors, that processor is the one that has taken the proper direction for convergence.

Traditionally, radix-2 based number representation systems have been used for both the redundant and non-redundant CORDIC algorithm. There have been numerous publications that use higher order radix representations (radix-4, 8) [24] [25] [26] [27] and very-high radix (radix-512) [28]. These representations allow for more bits of the result to be calculated in a single iteration and hence, reduce the required number of iterations. A higher order radix r is always a power of two. The Arc Tangent Radix set is thus extended such that  $\alpha_i$  [ $\sigma_i$ ] =  $\arctan(\sigma_i r^{-i})$ , where  $\sigma_i \in \{-r/2, \ldots, 0, \ldots, r/2\}$ . Such a representation gives a redundant ATR representation of angles. For example, the radix-4 CORDIC pseudo-rotation equations would be rewritten as:

$$x_{i+1} = x_i - \sigma_i y_i 4^{-i} (2.72)$$

$$y_{i+1} = y_i + \sigma_i x_i 4^{-i} (2.73)$$

$$z_{i+1} = z_i - \sigma_i \arctan 4^{-i} \tag{2.74}$$

where  $\sigma_i \in \{-2, -1, 0, 1, 2\}$ . In a radix-4 implementation, the number of iterations required for the CORDIC algorithm are reduced by half. Two problems arise from the use of this new radix representation. First, the direction selection function for both the rotation and vectoring mode become quite complex because of the extended  $\sigma_i$  set of ATR digits. Second, this digit set will lead to a variable scaling factor.

Several solutions have been devised to both these problems, and can be found in [24] [25] [26] [27] [28].

#### 2.4 Convergence

When considering a particular variation of the CORDIC algorithm, it is important to ensure the correctness of the result and determine its limitations in terms of precision. Obviously, the precision of the result is determined by the width of the internal data paths. In the case of circular CORDIC, precision is determined by the maximum shift parameter S(N-1) and the smallest rotation angle  $\alpha_{N-1} = \arctan(2^{-S(N-1)})$ .

Convergence in both the rotation mode and the vectoring mode must also be ensured in order to obtain the correct result. In rotation mode, the z data path is being driven to zero, and there has to be enough angles remaining in subsequent iterations in order to bring the value of z within  $\alpha_{N-1}$  of zero. Thus, there exists a set  $\{\sigma_j\}$  where  $j=i,i+1,\ldots,N-1$  such that:

$$\left| z_i - \sum_{j=i}^{N-1} \sigma_j \alpha_j \right| \le \alpha_{N-1} \tag{2.75}$$

From this, we define the *range of convergence* which determines the angles that the CORDIC algorithm will be able to process in order to produce correct results. From Equation 2.75 it is easily shown that the range of convergence is given by:

$$|z_{in}| \le \sum_{i=0}^{N-1} \alpha_i + \alpha_{N-1} \tag{2.76}$$

When using conventional CORDIC, the shift sequence is  $\{S(i) = i\}$ , that is i = 0, 1, ..., N-1. The range of convergence is roughly [-1.7433, +1.7433] for N = 16. Two possible solutions exist in order to expand the range to  $[-\pi, +\pi]$ . The first solution is to perform pre-rotation by an angle of  $\frac{\pi}{2}$ . In this case, the pre-rotation

equations are given by:

$$x_0' = -\sigma x_0 \tag{2.77}$$

$$y_0' = \sigma y_0 \tag{2.78}$$

$$z_0' = z_0 + \sigma \frac{\pi}{2} \tag{2.79}$$

where  $\sigma = +1$  if y < 0, -1 otherwise. The second solution is to perform an initial rotation of either  $\pi$  or 0, as in the following equations:

$$x_0' = \sigma x_0 \tag{2.80}$$

$$y_0' = \sigma y_0 \tag{2.81}$$

$$z'_{0} = \begin{cases} z_{0} & \text{if } \sigma = 1, \\ z_{0} - \pi & \text{if } \sigma = -1 \end{cases}$$

(2.82)

where  $\sigma = +1$  if x < 0, -1 otherwise. From Equation 2.76, it is now possible to derive the *convergence criterion* for the CORDIC process. This criterion imposes a specific order on the angle shift sequence, and is given by:

$$|\alpha_i| \le \sum_{j=i+1}^{N-1} \alpha_j + \alpha_{N-1}$$

(2.83)

Similarly, the range of convergence in vectoring mode is related to the x and y input and is given by:

$$\left|\arctan\left(\frac{y_{in}}{x_{in}}\right)\right| \le \sum_{i=0}^{N-1} \alpha_i + \alpha_{N-1} \tag{2.84}$$

#### 2.5 Error Analysis

The finite nature of the CORDIC algorithm leads to errors in terms of precision when performing rotation and vectoring operations on the input data. The ideal CORDIC process data paths would have an infinite number of bits and the number of iterations would also be infinite. It is useful to use this theoretical model in order

to derive the error bounds for a particular hardware implementation. An in-depth discussion of the various errors related to the CORDIC algorithm can be found in [29] and [30], and only a brief overview will be provided. There are four main sources of error in the CORDIC process:

- 1. Input value rounding error

- 2. Angle approximation error

- 3. Iteration rounding error

- 4. Scaling factor compensation error

The input value rounding error occurs when the data path width is less than the input data width. Since the CORDIC process induces magnitude growth in the vector being rotated, the input value rounding error is also scaled as it propagates to the outputs.

The second type of error is due to the fact that the total rotation angle  $\theta$  is approximated by a linear combination of a limited set of ATR angles such that:

$$\theta = \sum_{i=0}^{N-1} \sigma_i \alpha_i + \delta \tag{2.85}$$

where  $\delta$  is the error due to the angle approximation. In order to minimize this error, it is important to make  $\alpha_{N-1}$  as small as possible. However, the width of the data path impose a lower bound on the value of  $\alpha_{(N-1)}$ . Since  $\alpha_{(N-1)} = \arctan 2^{(N-1)} \approx 2^{(N-1)}$ , this angle will be equal to the smallest representable value in the z data path.

The third type of error is due to the limited precision arithmetic of the shift and add operations within the pseudo-rotation equations for the x and y data paths. Rounding errors will occur every time a shifted operand is added (or subtracted) from a non-shifted operand. Once again, the errors due to rounding will incur growth from the moment they appear up to the end of the CORDIC process. Defining  $\epsilon$  as the machine accuracy and b as the number of bits for the x and y data paths, we have

$\epsilon = 2^{-b-1}$  in the case of rounding and  $\epsilon = 2^{-b}$  in the case of truncation. Thus, for n iterations, the accumulated error f(n) due to rounding is bounded by:

$$|f(n)| \le n\epsilon \tag{2.86}$$

Note that the scaling factor contribution has been neglected in this case.

The final type of error is due to the post-scaling multiplication of the inverse scaling factor with the final x and y values. Since the inverse scaling factor is also rounded, it has an associated error  $\Delta K^{-1}$ . Multiplication by the inverse scaling factor will be of the form:

$$x' + \Delta x' = (x + \Delta x) \cdot (K^{-1} + \Delta K^{-1}) \tag{2.87}$$

Using simple averaging errors, this error may be represented by:

$$\Delta x' = x \Delta K^{-1} + K^{-1} \Delta x \tag{2.88}$$

#### 2.6 Implementations on FPGA

In recent years, there has been increasing interest in FPGA implementations of the CORDIC algorithm. This is due in part to the trend back to hardware for Digital Signal Processing applications and the increase in logic density of modern programmable devices. Andraka [1] was one of the first to provide a practical overview of CORDIC algorithms specifically for FPGAs. The architectures discussed in the paper examined two different aspects for implementing the algorithm. In the first, an architecture could be either *iterative* or *pipelined*. The second aspect considers *bit-serial* and *bit-parallel* implementations. These different approaches may be combined together in a number of ways, and selecting the proper architecture for a particular application is a trade off between speed and area. The paper also discusses how these architectures are implemented at the Control Logic Block level for some specific devices. In order to optimize the performance of the CORDIC algorithm on an FPGA,

a designer must carefully decide how to use the available resources in the most efficient way; this is a very different approach compared to ASIC design. There have also been other similar studies [31] [32] [33] [34]. Some of these studies examined high-radix implementations [32] [34] and the use of Redundant Number System representations (RNS) [31] [33]. It is interesting to note that in [33], the authors conclude that an RNS implementation is not suitable for FPGA design. They stipulate that operators needed for the RNS implementation require a 4 to 5 times larger area than their conventional counterpart. Furthermore the speed advantages that are gained in a full custom design are lost in the FPGA design due to longer routing delays.

# 2.7 Summary

This chapter presented the basic CORDIC algorithm, along with the unified CORDIC algorithm capable of performing vector rotations for the circular, linear and hyberbolic coordinate systems. An overview of the most important ideas in order to speed up and/or simplify the algorithm were also presented. In the next chapter, the characteristics of the target FPGA will be examined in order to determine which type of CORDIC variant will be suitable for implementation on the chosen platform.

# CHAPTER 3: DESIGN CONSIDERATIONS

In order to design CORDIC processors optimized for a certain type of application, an understanding of the physical characteristics of the target platform is essential. In this particular case, the Field Programmable Gate Array (FPGA) will be used for the various processor implementations. The available resources will determine what type of algorithm and ultimately, what type of architecture, are most suitable for implementation on this particular platform.

#### 3.1 FPGA Architecture

The basic Field Programmable Gate Array (FPGA) is essentially an array of Configurable Logic Blocks (CLB). Each CLB contains programmable function generators and associated memory elements. They may be combined via wiring resources called the *routing channel*. The routing channel contains wires that run in both horizontal and vertical directions. Programmable elements allow for wire interconnects. Input/Output (I/O) ports are also accessible through the routing channel. In addition to these basic elements, an FPGA might contain other dedicated resources such as large blocks of RAM or built-in multipliers. For this project, the target platform is the Xilinx Virtex-II. Although a specific device was chosen, the proposed CORDIC processors are also adaptable for other programmable logic devices.

Following is a list of dedicated resources that are available on the Virtex-II:

- Programmable I/Os

- Digital Clock Manager blocks (DCMs)

- Dual Port Block Select RAM (18Kbit)

- Embedded 18x18 Multiplier blocks

- Control Logic Blocks (CLBs)

The CLB is the top level logic component and is made up of four slices. Each slice contains two logic cells, for a total of eight distinct logic cells per CLB. The logic elements available in a slice is of particular interest, since they will become the basic building blocks of an optimized design. Each Virtex-II slice contains the following:

- 2 Function Generators (FG)

- 2 Storage Elements

- Arithmetic Logic Gates

- Large Multiplexers

- Fast Carry Look-Ahead chain

- Horizontal Cascade Chain (OR gate)

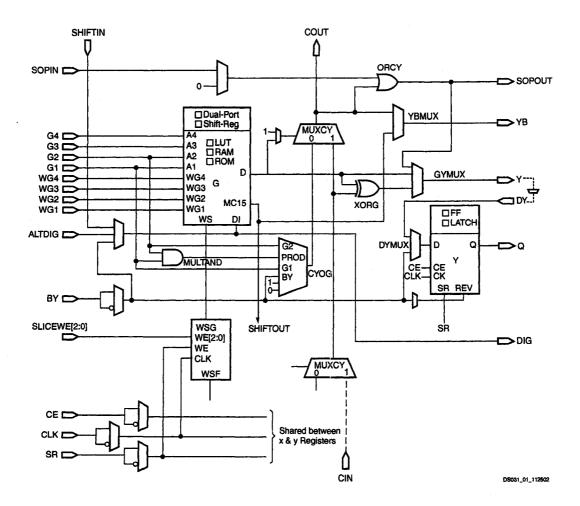

Figure 3.1 shows further details for a single logic cell and shows how these different elements are connected together. The most important logic element available in a cell is the Function Generator (FG). It can be configured as a Look-Up Table (LUT) that implements a 4:1 logic function. A second option is to use the FG as a 16-bit Variable Tap Shift Register. Finally, it can also be configured as 16-bit SelectRAM memory. It is also important to note that two 16-bit RAM resources can be combined together in order to provide dual port 16-bit RAM with one dedicated read/write port and a second read-only port.

# 3.2 Number System and Arithmetic for FPGA

As described in Chapter 2, considerable research has been conducted on the use of high-radix and redundant number systems for the CORDIC algorithm. The

Figure 3.1: Virtex II Logic Cell

motivation for using number systems other than two's complement is to reduce the carry propagation time of additions in order to increase throughput. In a signed digit representation, every digit requires two bits, effectively doubling the data path. Furthermore, use of these non-conventional systems leads to a non-constant scaling factor. Studies have shown that advantages gained in an ASIC design by using redundant number systems are lost when implemented on an FPGA because of the increase in number of logic blocks and routing delays [31] [33]. Use of higher-radix number systems was also found unsuitable for FPGA implementations [34].

The Fast Carry Logic available on the Virtex-II is intended for the two's complement number system, and allows for very fast arithmetic operations. These operations are carried out in a bit-parallel fashion, meaning that all the bits of the result are calculated at once by allowing the carry signal to propagate from the LSB to the MSB. Bit-serial arithmetic is an alternative way of performing such operations. Each operation is carried-out one bit at a time by reusing the same hardware. Although this is not as efficient in terms of speed, it does provide the potential for significant savings in terms of both logic cells and routing resources. Consider for example the storage elements included in a slice on the Virtex-II device. When a bit-parallel approach is used, only the 2 memory elements are usable for storage, meaning that a 16-bit register will require 8 slices for storage. In the bit-serial case, the entire register can fit in one LUT configured as a 16-bit shift register, requiring only half a slice. The 16 bit register requires virtually no wiring: only the input, output and clock lines are required. The drawback however is that a controller is required in order to perform bit-serial operations. Also note that in lower grade programmable devices that do not have fast carry-logic, the gap in performance between a bit-serial design and a bit-parallel design will be even smaller.

## 3.3 Design Goals

The main focus for this project is to provide CORDIC implementations suitable for System on Chip (SoC) that will fit on a single FPGA. As already mentioned, many applications will require a number of CORDIC processing elements. Thus, the CORDIC implementations are required to be compact and of low complexity. The fully pipelined bit-parallel implementation will obviously have the highest throughput compared to other approaches, but will require the most logic elements and routing resources. In applications such as audio processing that do not require extremely high data rates, such an approach will take up unnecessary real-estate. Providing alternative architectures and characterizing their area/performance trade offs provides designers with a wider range of options that will allow for the tightest possible integration of their design. Following are some of the important characteristics to examine when determining the most suitable CORDIC implementation for a particular application.

## 3.3.1 Latency

Latency is the amount of time required for the input to propagate to the output. Ideally, this amount of time is to be kept to a minimum. An iterative algorithm such as CORDIC has an inherently high latency as opposed to other methods such as look-up tables for calculating values of trigonometric functions. Some possible solutions to reducing latency are simplification of the algorithm and exploiting parallelism wherever possible.

# 3.3.2 Throughput

Throughput is the amount of data produced per unit of time. Pipelining is the most common way of increasing throughput. In order to have high throughput, the maximum delay between pipeline stages must be kept to an absolute minimum. In an iterative architecture, throughput is determined by the latency of the algorithm,

as well as the delay required for each iteration. Insuring the algorithm can complete in as few iterations as possible will maximize throughput in the case of an iterative architecture.

## 3.3.3 Accuracy and Error

Accuracy and allowable error are highly dependent on the application being targeted. Obviously, the automatic generation of a CORDIC PE architecture must allow for a wide range of accuracy requirements. Floating point implementations also allow for a greater dynamic range than fixed point implementations. For the CORDIC algorithm, one extra bit of accuracy is obtained for every iteration.

# 3.3.4 Area

The area occupied by a CORDIC PE becomes a crucial design consideration if the PE is to be used as part of a larger design, such as systolic array or a system on chip (SoC). Architectures that use the minimum number of logic blocks and minimize the number of required interconnects will ensure that the PE does not take up too much valuable real estate on the FPGA.

#### 3.3.5 Power Consumption

With the increase in integration, larger FPGAs and portable systems, power consumption is becoming an important issue. Obviously, implementation must be as simple as possible in order to reduce unnecessary power consumption. Cutting down on long interconnects and minimizing fanout are crucial in bringing down power consumption in an FPGA. This is usually accomplished by inserting memory elements to break up the interconnect and reduce the fanout. Reducing unnecessary glitches with the use of appropriate state-machine memory elements will also help to reduce power dissipation. Finally, power consumption can be reduced by preventing unnecessary switching and turn off parts of a circuit when they are not required.

# 3.3.6 Scalability

Scalability is the ability of a system to be extended in order to meet increasing requirements while minimizing impacts on performance. In the case of the CORDIC PE, scaling will imply that various bitwidths must be supported in order to be suitable for a wide range of applications. It is important to note that the performance and complexity of the CORDIC algorithm is directly proportional to its required accuracy.

## 3.4 Architectural Styles

The internal structure of FPGAs in general lends itself to a certain number of architectural styles. For this work, four broad categories will be examined, namely bit-parallel iterative, bit-parallel pipelined, bit-serial iterative and bit-serial pipelined.

## 3.4.1 Bit-Parallel Iterative Architecture

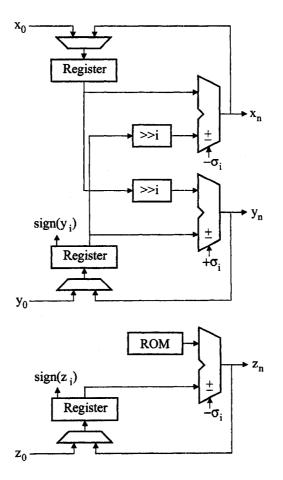

The bit-parallel iterative structure stems directly from the CORDIC pseudorotation equations, and is shown in Figure 3.2. Initial values are loaded into the appropriate registers via the input multiplexers. Two barrel shifters are required in order to provide the shifted values for  $x2^{-i}$  and  $y2^{-i}$  for the cross-additions. The ATR constants for the z data path are stored in ROM and the outputs of the x, y and z data paths are fed back into their respective registers. The direction of rotation  $\sigma_i$  is determined by the sign of the z register in rotation mode or the sign of the y register in vectoring mode. A controller (omitted on the figure) is required in order to provide the ROM addresses and and shift parameters to the barrel shifters.

This design is relatively compact and straight forward. Implementing efficient barrel-shifters is an important issue for this architecture in order to maximize the use of available logic elements. For bit-parallel implementations, the latency is equal to the number of iterations  $N_{iter}$ . If  $F_{clock}$  is the maximum operating frequency of the

Figure 3.2: Bit-Parallel Iterative CORDIC Structure [1]

iterative processor, then the throughput R will be:

$$R = \frac{F_{clock}}{N_{iter}} \tag{3.1}$$

# 3.4.2 Bit-Parallel Pipelined Architecture

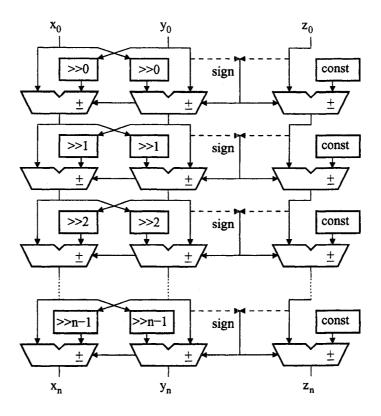

By unrolling the iterative architecture, a purely combinational structure as depicted in Figure 3.3 can be obtained. This type of structure does not require barrel shifters since the shift for the cross adders are provided by the wiring. The

Figure 3.3: Unrolled Bit-Parallel CORDIC Processor [1]

ROM is also eliminated, as each ATR constant required in the z data path can now be hardwired. The suppression of the barrel shifters and ROM also leads to the elimination of the controller. The design is easily pipelined by adding registers after each adder/subtracter. In an FPGA, each logic cell has an associated memory element. If only the logic cell are used, the memory elements are lost. Thus, pipelining in an FPGA comes at no extra cost, and should be exploited wherever possible. In this case, the throughput R is:

$$R = F_{clock} \tag{3.2}$$

Figure 3.4: Bit-Serial Iterative CORDIC [1]

# 3.4.3 Bit-Serial Iterative Architecture

The bit-serial iterative architecture is depicted in Figure 3.4. By processing the bits one at a time, there is no delay associated with carry propagation and a lot less hardware is required for the adders. In this manner, the processor can have a higher clock rate. However, the wide multiplexer can present problems for implementations in certain FPGAs. The controller required for such an architecture is more complex than for a bit-parallel design, since the bit-serial addition has to be properly sequenced. This usually requires insertion of a few delay memory elements in order to properly align the control signals and reset the serial adder carry storage. Denoting  $B_{eff}$  as the number of effective bits in the register and  $B_{delay}$  as the number of delay bits, the throughput of the bit-serial processor will be:

$$R = \frac{F_{clock}}{N_{iter} \cdot (B_{eff} + B_{delay})} \tag{3.3}$$

Figure 3.5: Bit-Serial Pipelined CORDIC

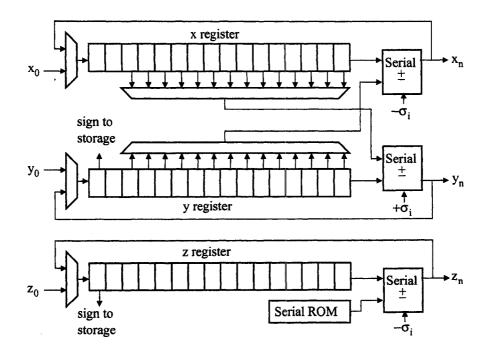

# 3.4.4 Bit-Serial Pipelined Architecture

The bit-serial iterative structure can also be unrolled into a pipelined architecture, as shown in Figure 3.5. The serial ROMs will become one-dimensional as opposed to the two-dimensional ROM required for the iterative architecture. Also, the wide multiplexer is no longer required since all registers contain a tap for the corresponding shift value. As the bits are fed continuously into the next register, some mechanism for sign recording and sign extension is also required. Some form of sequencing is necessary in order to handle sign recording, sign extension, serial ROM addressing and serial addition. The throughput for such an architecture will be:

$$R = \frac{F_{clock}}{(B_{eff} + B_{delay})} \tag{3.4}$$

# 3.5 Xilinx Intellectual Property Core

Xilinx already provides an Intellectual Property (IP) CORDIC implementation as part of their LogiCORE product line. These cores can be built automatically through the Xilinx Core Generator interface according to user supplied parameters. The implementations are specially tailored to Xilinx FPGAs and utilize the available

logic elements in an extremely efficient way. The version used during the course of this project was the CORDIC v2.0. In this version, only the bit-parallel iterative and pipelined architectures can be generated. These implementations use the original CORDIC equations with a very fast and area efficient constant coefficient multiplier (CCM) for scaling factor compensation. The generated CORDIC cores will be used as benchmarks for the processing elements proposed in this work.

# 3.6 Summary

This chapter outlined the key characteristics of the Xilinx Virtex-II, which will be the target platform used for this project. The design goals for the CORDIC Processing Elements were also outlined. Finally, the four broad architectural styles that will form the basis for the CORDIC PEs have been examined, namely the bit-parallel iterative, bit-parallel pipelined, bit-serial iterative, and bit-serial pipelined architectures. In the next chapter, these design considerations will be used in order to select a suitable CORDIC algorithm for implementation on the Virtex-II device.

# CHAPTER 4: ALGORITHM SELECTION

The original algorithm proposed by Volder [2] is the most common way of implementing CORDIC in hardware. Since each pseudo-rotation is dependent on the previous result, the rotation stages offer little parallelism opportunities. Hybrid radix representation and rotation prediction provide an alternative, but are only valid in the case of rotation. Decreasing latency in a pipelined architecture thus becomes a matter of implementing an extremely efficient Constant Coefficient Multiplier, as is the case for the Xilinx CORDIC IP Core. However, the iterative structure and bit-serial architectures have different characteristics, and the most efficient approach for a parallel pipelined architecture might not be suitable in these other circumstances. In this chapter, two potential candidates will be compared and the most suitable algorithm will be selected in order to implement the CORDIC PE on an FPGA.

# 4.1 Double Shift CORDIC

The double shift CORDIC technique was first discussed in [35]. Instead of performing a single shift on the  $x_i$  and  $y_i$  variables, two different shift values are obtained and are either added or subtracted. This allows added flexibility in the angles that are used for each iteration, and angle shift parameters are chosen in such a way that the scaling factor is steered toward a simple sum of signed powers of two. Originally, parameter optimization was considered in order to produce a general purpose ALU capable of performing rotations in all three coordinate systems, i.e. linear, circular and hyperbolic. Similar results were also presented in [36]. In [37], sets of shift parameters are presented that are optimized only for the circular case. Furthermore, [36] and [37] consider scaling factors that are simple sums (or differences) of signed powers of two containing 2 terms, whereas [35] only considers a

scaling factor of 0.5 for the circular coordinate system.

The modified iteration equations for the Double Shift CORDIC algorithm are as follows:

$$x_{i+1} = x_i - \sigma_i (2^{-S(i)} + \eta(i)2^{-S'(i)}) y_i$$

(4.1)

$$y_{i+1} = y_i + \sigma_i (2^{-S(i)} + \eta(i)2^{-S'(i)}) x_i$$

(4.2)

$$z_{i+1} = z_i - \sigma_i \alpha_i \tag{4.3}$$

where:

$$\alpha_i = \arctan(2^{-S(i)} + \eta(i)2^{-S'(i)})$$

(4.4)

Notice that each angle is now described by three parameters, S(i), S'(i) and  $\eta(i)$ . The parameter S'(i) is a second shift factor, and  $\eta(i) \in \{-1,0,1\}$ . Thus, the equations for the x and y data paths now contain two shifting operations and two addition operations. The z data path is unaffected since the  $\alpha_i$  constants are pre-calculated. The following constraints are also imposed on the shift parameters:

1. Angle set:

$$\alpha_i = \arctan(2^{-S(i)} + \eta_i 2^{-S'(i)})$$

(4.5)

where:

$$\eta_i \in \{-1, 0, 1\}$$

$$S(i), S'(i) \in \{0, 1, \dots, N\}$$

$$S'(i) > S(i)$$

2. Representation range:

$$\sum_{i=0}^{N} \alpha_i \ge \frac{\pi}{2} \tag{4.6}$$

3. Angle convergence:

$$\alpha_i \le \alpha_N + \sum_{j=i+1}^N \alpha_j \text{ for } i = 0, \dots, N-1$$

(4.7)

4. Angle precision:

$$\alpha_N = \arctan(2^{-N}) \tag{4.8}$$

5. Inverse scaling factor composition:

$$K^{-1} = \prod_{i=0}^{N} \cos \alpha_i \approx \sum_{j=0}^{D-1} \lambda_j 2^{-T_j}$$

(4.9)

$$\lambda_j \in \{-1, 0, +1\} \tag{4.10}$$

$$T_j \in \{0, \dots, N\}$$

(4.11)

The resulting scaling factor is given by:

$$K = \prod_{i=0}^{N-1} \sqrt{1 + 2^{-2S(i)} + \eta_i 2^{-S(i) - S'(i) + 1} + \eta_i^2 2^{-2S'(i)}}$$

(4.12)

The derivation of the scaling factor is given in Appendix A.

In (4.9), D indicates the maximum number of signed digits. The above constraints are required in order to preserve the convergence properties and the accuracy of the CORDIC process. Finding shift parameters that will yield a simple inverse scaling factor is an optimization problem where the total number of iterations has to be kept to a minimum and the number of iterations where  $\eta_i \neq 0$  also has to be minimum. Furthermore, limits have to be imposed on how many double shift iterations and how many total iterations that can be used as the ATR. Note also that according to [38], this problem is NP-complete.

In order to further investigate the properties of the Double Shift CORDIC and its usefulness for hardware implementations, a study was conducted as part of this thesis and published in [39]. In this study, a more flexible solution in terms of optimization is proposed for both recursive and pipelined architectures. Particularly, the use of modified CORDIC ATR sequences was carefully considered against the basic CORDIC algorithm originally proposed by Volder [2] and Double Shift CORDIC shift sequences presented in [40] in order to ensure that benefits are achieved in terms of area, power, and throughput. The proposed approach was to allow more flexibility