# An Architecture for the AES-GCM Security Standard

by

# Sheng Wang

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2006

©Sheng Wang 2006

# **Author's Declaration**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

### **Abstract**

The forth recommendation of symmetric block cipher mode of operation SP800-38D, *Galois/Counter Mode of Operation* (GCM) was developed by David A McGrew and John Viega. GCM uses an approved symmetric key block cipher with a block size of 128 bits and a universal hashing over a binary Galois field to provide confidentiality and authentication. It is built specifically to support very high data rates as it can take advantage of pipelining and parallel processing techniques.

Before GCM, SP800-38A only provided confidentiality and SP800-38B provided authentication. SP800-38C provided confidentiality using the counter mode and authentication. However the authentication technique in SP800-38C was not parallelizable and slowed down the throughput of the cipher. Hence, none of these three recommendations were suitable for high speed network and computer system applications.

With the advent of GCM, authenticated encryption at data rates of several Gbps is now practical, permitting high grade encryption and authentication on systems which previously could not be fully protected. However there have not yet been any published results on actual architectures for this standard based on FPGA technology.

This thesis presents a fully pipelined and parallelized hardware architecture for AES-GCM which is GCM running under symmetric block cipher AES on a FPGA multi-core platform corresponding to the IPsec ESP data flow.

The results from this thesis show that the round transformations of confidentiality and hash operations of authentication in AES-GCM can cooperate very efficiently within this pipelined architecture. Furthermore, this AES-GCM hardware architecture never unnecessarily stalls data pipelines. For the first time this thesis provides a complete FPGA-based high speed architecture for the AES-GCM standard, suitable for high speed embedded applications.

# **Acknowledgements**

I would like to thank my supervisor, Professor Cathy Gebotys, for all her advices, guidance and encouragement. I would also like to thank Ann Lee, Suze Yang, my parents and brothers for their love and support.

I greatly appreciate the scholarships awarded to me by the Natural Sciences and Engineering Research Council of Canada (NSERC), the University of Waterloo, and the Department of Electrical and Computer Engineering at the University of Waterloo.

I am also grateful for the perfect campus environment provided by *the University of Waterloo*. On the campus, I enjoy not only the various academic activities, but also the diverse sports, such as swimming, golf, squash, volleyball, aerobics, curling and juggling.

# **Table of Contents**

| Author's Declaration                                            | ii  |

|-----------------------------------------------------------------|-----|

| Abstract                                                        | iii |

| Acknowledgements                                                | iv  |

| Table of Contents                                               | V   |

| List of Tables                                                  | vii |

| List of Figures                                                 | ix  |

| Chapter 1 Introduction.                                         | 1   |

| 1.1 Motivation                                                  | 1   |

| 1.2 Work Objective                                              | 2   |

| 1.3 Thesis Organization                                         | 3   |

| Chapter 2 Background                                            | 5   |

| 2.1 Mathematical Background                                     | 5   |

| 2.1.1 Finite Fields                                             | 5   |

| 2.1.2 Operations over Binary Finite Fields GF (2 <sup>m</sup> ) | 7   |

| 2.2 Confidentiality Mode of Operation Background                | 13  |

| 2.2.1 Electronic Codebook Mode (ECB)                            | 13  |

| 2.2.2 Counter Mode (CTR)                                        | 14  |

| 2.3 Field Programmable Gate Arrays (FPGA)                       | 16  |

| 2.3.1 Advantages of FPGA in Cryptographic Applications          | 16  |

| 2.3.2 FPGA VirtexII pro xc2vp100                                | 17  |

| 2.4 The CMC-Prototyping Platform                                | 24  |

| Chapter 3 Security Standard                                     | 29  |

| 3.1 Advanced Encryption Standard (AES)                          | 29  |

| 3.1.1 AES Cipher.                                               | 30  |

| 3.1.2 Key Expansion.                                            | 34  |

| 3.2 Galois/Counter Mode (GCM)                                   | 35  |

| 3.2.1 Block Cipher                                              | 35  |

| 3.2.2 Input and Output Data                                     | 36  |

| 3.2.3 Types of Applications of GCM                              | 37  |

| 3.2.4 GHASH Function                                            | 37  |

| 3.2.5 GCTR Function                                             | 39  |

| 3.2.6 GCM Specification                                | 41  |

|--------------------------------------------------------|-----|

| Chapter 4 The Architecture of AES-GCM                  | 45  |

| 4.1 Modules Design                                     | 45  |

| 4.1.1 AES Module                                       | 45  |

| 4.1.2 GHASH Module                                     | 48  |

| 4.2 High Speed Hardware Implementation of AES-GCM      | 50  |

| 4.2.1 Format of Data Packet of IPsec ESP               | 50  |

| 4.2.2 Data Flow in GCM                                 | 52  |

| 4.2.3 Hardware Implementation Bidirectional GCM        | 54  |

| 4.3 Verification of AES-GCM Functionality              | 57  |

| 4.3.1 IPsec Signal Generator                           | 57  |

| 4.3.2 Verifying Both AES-GCM-AE and AES-GCM-AD on FPGA | 58  |

| 4.4 Comparison with Other Research                     | 60  |

| Chapter 5 Concluding Remarks                           | 63  |

| 5.1 Summary and Contributions                          | 63  |

| 5.2 Future Work                                        | 64  |

| Appendix A Test-Vectors for AES-GCM [12]               | 67  |

| Appendix B Package for AES-GCM VHDL Codes              | 69  |

| Appendix C VHDL Codes for AES-GCM modules              |     |

| Appendix D Test-bench for the GCM module               | 101 |

| Appendix E VHDL Codes of IPsec ESP Signal Generator    | 105 |

| Appendix F The Critical Path on GCM module             | 113 |

# **List of Tables**

| Table 1. Virtex-II Pro Resources                                  | 18 |

|-------------------------------------------------------------------|----|

| Table 2. Resources Used by Distributed Memory [15]                | 20 |

| Table 3. Block SelectRAM Configuration Modes [15]                 | 23 |

| Table 4. Key-Block-Round Combinations [3]                         | 29 |

| Table 5. Round Constant Bytes, RC in Hexadecimal [18]             | 35 |

| Table 6. Comparison between Iterative and Pipelined AES           | 46 |

| Table 7. Comparison between Different GHASH Architectures         | 49 |

| Table 8. AES-GCM Implementations on Block RAM and Distributed RAM | 56 |

| Table 9. AES-GCM Implementation Results                           | 61 |

# **List of Figures**

| Figure 1. Bit Serial Multiplier over GF(2 <sup>m</sup> )                                                                              | 9  |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2. Architecture of Bit Parallel Multiplier over GF(2 <sup>m</sup> ).[17]                                                       | 11 |

| Figure 3. ECB Encryption and ECB Decryption [1]                                                                                       | 13 |

| Figure 4. CTR Encryption and CTR Decryption [1]                                                                                       | 15 |

| Figure 5. General Slice in Virtex-ll Pro [15]                                                                                         | 19 |

| Figure 6. Single-Port Distributed SelectRAM+ [15]                                                                                     | 21 |

| Figure 7. Dual-Port Distributed SelectRAM+ [15]                                                                                       | 22 |

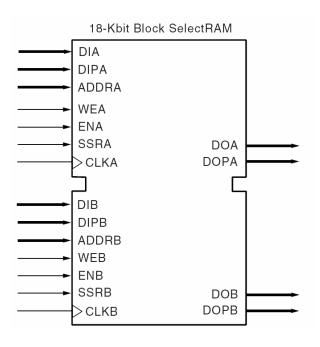

| Figure 8. Block SelectRAM in Single-Port Mode [15]                                                                                    | 23 |

| Figure 9. Block SelectRAM in Dual-Port Mode[15]                                                                                       | 24 |

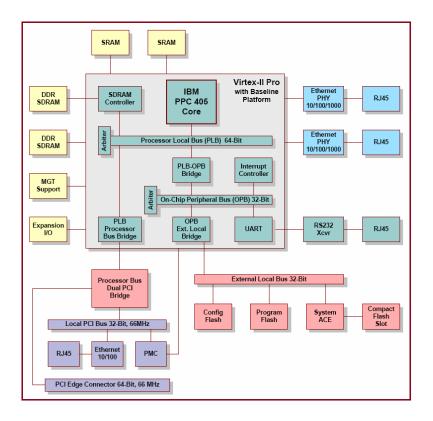

| Figure 10. AP1100 Board Architecture [24]                                                                                             | 27 |

| Figure 11. Illustration of State Array [3]                                                                                            | 30 |

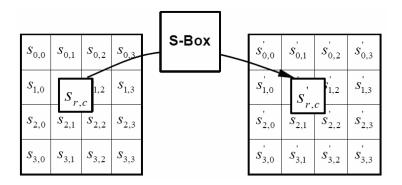

| Figure 12. Illustration of SubBytes Operation [3]                                                                                     | 31 |

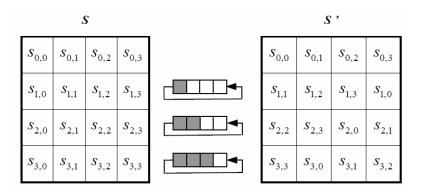

| Figure 13. Illustration of ShiftRows Transformation [3]                                                                               | 32 |

| Figure 14. AES Forward Cipher Operation (Pipelining Data Path)                                                                        | 33 |

| Figure 15. Key Expansion [18]                                                                                                         | 34 |

| Figure 16. GHASH <sub>H</sub> (X1    X2       Xm) = Ym.[2]                                                                            | 38 |

| Figure 17. GCTR <sub>K</sub> (ICB, X1 $\parallel$ X2 $\parallel$ $\parallel$ X*n) = Y1 $\parallel$ Y2 $\parallel$ $\parallel$ Y*n.[2] | 40 |

| Figure 18. AES-GCM-AE <sub>K</sub> (IV, P, A) = $(C, T)$ .[2]                                                                         | 42 |

| Figure 19. AES-GCM-AD <sub>K</sub> (IV, C, A, T) = P or FAIL.[2]                                                                      | 44 |

| Figure 20. AES Iterative Data Path                                                                                                    | 46 |

| Figure 21. AES CTR over ECB Mode Cipher Structure                                                                                     | 47 |

| Figure 22. GHASH Hardware Architecture                                                                                                | 48 |

| Figure 23. Format of Data Packet of IPsec ESP.                                                                                        | 51 |

| Figure 24. The Use of GCM in IPsec ESP[11]                                                                                            | 51 |

| Figure 25. (a) The Data Flow of GCM Encryption (b) The Data Flow of GCM Decryption                                                    | 53 |

| Figure 26. AES-GCM Encryption Architecture                                                                                            | 55 |

| Figure 27. 16-bit LFSR for IPsec ESP Signal Generator                                                                                 | 58 |

| Figure 28. AES-GCM Verification System                                                                                                | 59 |

| Figure 29. AES-GCM Hierarchical HDL Codes Design                                                                                      | 60 |

| Figure 30. Illustration How AES-GCM Works in Base-line Mode                                                                           | 65 |

# **Chapter 1**

### Introduction

### 1.1 Motivation

Since 2001, the National Institute of Standards and Technology (NIST) has published a total of four recommendations for Block Cipher Modes of Operation, specifically SP800-38A[1], SP800-38B[21], SP800-38C[22], and SP800-38D[2]. A block cipher mode of operation is an algorithm that uses a symmetric key block cipher to provide confidentiality, authentication or both for information security.

In SP800-38A, NIST recommends five confidentiality modes of operation for use with an underlying symmetric key block cipher algorithm: Electronic Codebook (ECB) mode, Cipher Block Chaining (CBC) mode, Cipher Feedback (CFB) mode, Output Feedback (OFB) mode, and Counter (CTR) mode. These five modes can be separated into two groups: one is a non-feedback mode group, including ECB and CTR; one is a feedback mode group, including CBC, CFB and OFB. In the feedback modes, the current computation/execution step depends on the result of the previous step. Therefore, to implement these kinds of modes in hardware, an iterative architecture is typically adapted for low throughput requirements rather than a pipelined architecture. In contrast, the use of ECB or CTR mode, or non-feedback modes, supports pipelined or parallelized architecture designs for processing high-speed data flows.

In SP800-38B, NIST recommends a message authentication code (MAC) algorithm that is based on a symmetric key block cipher. This cipher-based MAC is referred to as CMAC, or the Cipher Block Chaining MAC algorithm (CBC-MAC).

In SP800-38C, NIST recommends a mode of operation, called CCM, based on an approved symmetric key block cipher algorithm whose block size is 128 bits. CCM provides the confidentiality and the authenticity of data by combining the techniques of the CTR mode and the CBC-MAC.

The throughput of the CTR mode implementation, which can be pipelined, is much larger than that of CBC-MAC implementation, which can not be parallelizable. Specifically, none of these three recommendations, SP800-38A, B, and C, can be adapted for high speed network and computer system applications. Therefore, there is a compelling need for a mode of operation which can not only efficiently provide confidentiality, but authentication at high speed.

As the forth security standard of Block Cipher Mode of Operation, SP800-38D, *Galois/Counter Mode of Operation (GCM)*, fills the need above. GCM features the use of an approved symmetric key block cipher with a block size of 128 bits and a universal hash function that is defined over a binary Galois field. The most recently approved symmetric key block cipher with a block size of 128 bits is the Advanced Encryption Standard (AES) algorithm that is specified in Federal Information Processing Standard (FIPS) Pub.197 [3]. The specified universal hash function in GCM is defined over a binary Galois field (GF) and is a 128-bit polynomial multiplier over GF (2<sup>128</sup>), called GHASH. GHASH can provide a secure, parallelizable, and efficient authentication mechanism. For the confidentiality mechanism of GCM, the CTR mode embedded by ECB mode, called GCTR, is adopted using an underlying block cipher. GCM, i.e. SP800-38D, was officially published in April 2006. However there are no known FPGA (field programmable gate array) architectures or implementations of this standard.

# 1.2 Work Objective

The motivation behind this thesis is to demonstrate and analyze GCM's practical performance and area cost by implementing it on a realistic hardware platform. In the rest of this thesis, AES-GCM will refer to GCM with AES as the symmetric block cipher.

Presented in this thesis are the hardware architectures for AES-GCM, including iterative-AES module, pipelined-AES module, GHASH module, and Key-expanded module. These GCM elements are then integrated together along with control logic to implement the entire new security standard, AES-GCM.

To verify the feasibility, efficiency and cost of each hardware module in AES-GCM, AES-GCM has been demonstrated using an advanced multi-core FPGA. The architectural design was synthesized, timing simulated, and downloaded to the FPGA prototype platform.

# 1.3 Thesis Organization

This thesis is organized as follows: Chapter 2 gives an overview of the mathematical definitions over GF and confidentiality mode of operation concepts used in AES-GCM. This chapter also provides an introduction to the FPGA device structures and the FPGA prototype platform system used to create AES-GCM. Chapter 3 presents security standards, AES, and GCM. In chapter 4, the proposed hardware architectures of AES-GCM are presented. The bit parallel multiplier over GF, and the pipelined AES discussed in chapter 2 and 3 are chosen as the modules to build AES-GCM. A methodology, discussed in chapter 4, to verify the AES-GCM hardware implementation is established relying on the prototype platform. Finally, chapter 5 provides summary and future work.

# **Chapter 2**

# **Background**

This chapter provides the concepts necessary in order to understand GCM: Section 2.1 introduces to the concepts of finite fields, and the polynomial multiplier over binary finite fields followed by a discussion of its different implementation architectures. Section 2.2 is a description of ECB and CTR modes of operation which are the core of confidentiality of AES-GCM. Section 2.3 is an overview of FPGA technology and the multi-core FPGA prototype platform used to implement AES-GCM in this thesis.

# 2.1 Mathematical Background

The fundamentals of AES and GHASH are based on operations over the finite field. This section provides an introduction to these operations. The concepts and methods have been gathered from [4], [5], and [6].

### 2.1.1 Finite Fields

A field can be considered as a set whose elements form a group G under two operations: multiplication indicated by symbol "·" and addition indicated by symbol "+". These operations obey the basic algebraic properties. The relative finite field concepts are list as follows:

**Concept 1**.  $(F, +, \cdot)$  is a field if the following properties hold:

- The elements of F form a group under addition.

- The non-zero elements of F form a group under multiplication.

- The addition and multiplication operations are commutative, i.e. x + y = y + x and xy = yx for all  $x, y \in F$ .

• The multiplication operation can be distributed through the addition operation, i.e.  $x \cdot (y + x) = x \cdot y + x \cdot z$  for all x, y, and  $z \in F$ .

Concept 2. A field F with a finite number of elements is a finite field.

**Concept 3**. A non-zero element of a finite field F is said to be a primitive element or generator of F if its powers cover all nonzero field elements.

**Concept 4**. A unique finite field exists for every prime number. These fields are denoted GF(p<sup>m</sup>) where p is prime and m is a positive integer. One kind of field which is commonly used in cryptography applications is the binary finite fields GF(2<sup>m</sup>) where m is a large integer.

Concept 5. A basis for GF (2<sup>m</sup>) over GF(2) is a set of m linearly independent elements of GF(2<sup>m</sup>). Any element of GF(2<sup>m</sup>) can be represented as an algebraic sum of the basis elements.

The binary field  $GF(2^m)$  contains  $2^m$  elements. Each element is represented by the selected basis. The most common representation is based on polynomial basis. With the polynomial basis  $\alpha = \{1, \alpha, \alpha^2, ..., \alpha^{m-1}\}$ , the elements of  $GF(2^m)$  can be represented as polynomial of degree m-1 as follows:

$$GF(2^m) = \{A | A = a_0 + a_1\alpha + \dots + a_{m-1}\alpha^{m-1}, \text{ where } a_j \in GF(2), 0 \le j \le m-1\}$$

where  $\alpha$  is the root of any irreducible polynomial F(x) of degree m over GF(2).

Let

$$F(x) = 1 + f_1 x + f_2 x^2 + \dots + f_{m-1} x^{m-1} + x^m$$

where  $f_i \in GF(2)$ ,  $0 \le i \le m-1$ . The irreducible polynomial F(x) is often referred to as the field polynomial. The arithmetic in AES-GCM is based on polynomial basis and uses the polynomial  $F(x) = 1 + x + x^2 + x^7 + x^{128}$  as field polynomial.

# 2.1.2 Operations over Binary Finite Fields GF (2<sup>m</sup>)

Both operations, field addition and field multiplication, map a pair of field elements A and B onto another field element C, all A, B, and  $C \in GF(2^m)$ . The following introduction on field addition and multiplication is based on polynomial basis. The field elements A, B, and C are the following polynomials, respectively:

$$A(\alpha) = a_0 + a_1 \alpha + \cdots + a_{m-1} \alpha^{m-1}$$

$$B(\alpha) = b_0 + b_1 \alpha + \cdots + b_{m-1} \alpha^{m-1}$$

$$C(\alpha) = c_0 + c_1 \alpha + \cdots + c_{m-1} \alpha^{m-1}.$$

### 2.1.2.1 Field Addition

Over a finite field GF(2<sup>m</sup>), a field addition of two elements A and B consists of adding the two polynomials together. Because the coefficients in A and B are over GF(2) and each pair of coefficients are added independently, their sum C is written as

$$C(\alpha) = A(\alpha) + B(\alpha) = \sum_{i=0}^{m-1} (a_i + b_i)\alpha_i.$$

(1)

The pair of coefficients addition  $a_i + b_i$  in (1) is performed modulo 2 and translated to an exclusive- OR (XOR) operation in FPGA technology. That is to say that the field addition in (1) is computed by an m-bit XOR operation and does not require a carry chain.

### 2.1.2.2 Field Multiplication

Field multiplication over a finite field  $GF(2^m)$  is executed by straightforward multiplying two polynomials  $A(\alpha)$  and  $B(\alpha)$ , then dividing the resulting 2m-bit polynomial by  $F(\alpha)$ ; the m-bit remainder is the result  $C(\alpha)$ . The product C of field elements A and B is expressed as

$$C(\alpha) = A(\alpha) \times B(\alpha) \mod F(\alpha) = \sum_{i=0}^{m-1} c_i \alpha_i = \sum_{i=0}^{m-1} \sum_{j=0}^{m-1} a_j b_j \alpha^{i+j} \mod F(\alpha)$$

(2)

Commonly, people implement field multiplication in three methods with various efficiencies: Bit Serial multiplier, Bit Parallel multiplier and Digital Serial multiplier. In the following sections, the corresponding Algorithms to these three multipliers are presented.

### 2.1.2.2.1 Bit Serial Multiplier

By expanding  $B(\alpha)$  and distributing  $A(\alpha)$  to  $B(\alpha)$ 's terms in (2),  $C(\alpha)$  changes to

$$C(\alpha) = b_{m-1}\alpha^{m-1}A(\alpha) + \cdots + b_1\alpha A(\alpha) + b_0A(\alpha) \mod F(\alpha).$$

By repeatedly grouping and factoring out  $\alpha$ ,  $C(\alpha)$  changes further to

$$C(\alpha) = (\cdots (((A(\alpha)b_{m-1})\alpha + A(\alpha)b_{m-2})\alpha + \cdots + A(\alpha)b_1)\alpha + A(\alpha)b_0) \mod F(\alpha)$$

(3)

Starting with the inner most parentheses and moving out, Algorithm 1 performs the operation iteratively to compute the right hand side of (3). This algorithm can be used to compute the product of  $A(\alpha)$  and  $B(\alpha)$  in bit-level.

### **Algorithm 1** Bit-Serial Multiplication

Input:  $A(\alpha)$ ,  $B(\alpha)$ , and  $F(\alpha)$

Output:  $C(\alpha) = A(\alpha) \times B(\alpha) \mod F(\alpha)$

- 1.  $C(\alpha) \leftarrow 0$

- 2. for i = m 1 downto 0 do

- 3.  $C(\alpha) \leftarrow \alpha C(\alpha) \mod F(\alpha)$

- 4. if  $(b_i = 1)$  then

- 5.  $C(\alpha) \leftarrow C(\alpha) + A(\alpha)$ .

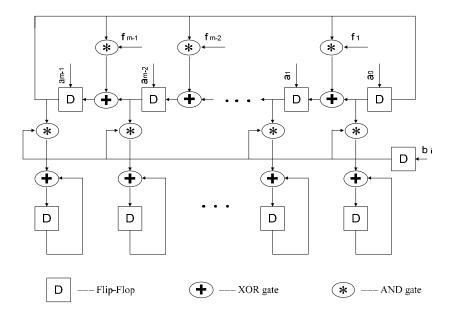

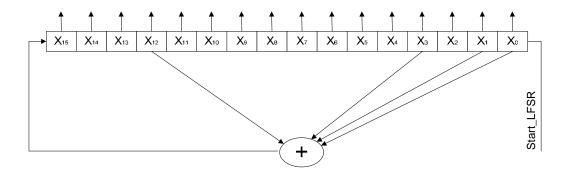

The Bit Serial multiplier is a direct implementation of Algorithm 1. Totally 128 clock cycles are needed for calculating a multiplication over  $GF(2^{128})$  if  $A(\alpha)$  can be loaded in parallel. The Figure 1 is the hardware structure of the bit serial multiplier.

Figure 1. Bit Serial Multiplier over GF(2<sup>m</sup>)

### 2.1.2.2.2 Bit Parallel Multiplier

Compared to the bit serial multiplier which needs m clock cycles to complete a multiplication over  $GF(2^m)$ , a bit parallel multiplier can complete computation in only 1 clock cycle over the same GF. (Because the circuit delays are very different between the bit serial multiplier and the bit parallel multiplier, the minimum clock period of clock for parallel multiplier is much larger than the minimum one for serial multiplier. i.e., 1 clock cycle computation time for parallel multiplier should be roughly equal to several or tens clock cycles computation time for serial multiplier.) A dedicated polynomial basis finite field bit parallel multiplier has been proposed in [6], called the Mastrovito multiplier. This multiplier is adapted to a fixed field polynomial  $F(\alpha)$ . The implementation procedure of the Mastrovito multiplier is described as follows.

First, rewrite polynomial elements A, B, and C in coefficient vector format as

$$A=(a_0, a_1, \cdots, a_{m-1}),$$

$$B=(b_0, b_1, \cdots, b_{m-1}),$$

and

$$C = (c_0, c_1, \dots, c_{m-1}).$$

Similarly, let

$$\alpha^i A = ((\alpha^i A)_0, (\alpha^i A)_1, \dots, (\alpha^i A)_{m-1}).$$

Then, rewrite the field multiplication equation (2) in matrix-vector form multiplication as follows:

$$C(\alpha) = \sum_{i=0}^{m-1} c_i \alpha_i = A(\alpha) \times B(\alpha) = A(b_0 + b_1 \alpha + \cdots + b_{m-1} \alpha^{m-1})$$

$$= (A, A\alpha, A\alpha^{2}, ..., A\alpha^{m-1}) \cdot B^{T}$$

(4)

Equate the coefficients of  $\alpha^i$ , i=0, 1, ..., m-1, on both sides of equation (4),

$$c_0 = ((A)_0, (\alpha A)_0, \dots, (\alpha^{m-1} A)_0) \cdot B^T$$

$$c_1 = ((A)_1, (\alpha A)_1, \dots, (\alpha^{m-1} A)_1) \cdot B^T$$

.

.

.

$$c_{m\text{-}1} = ((\ A)_{m\text{-}1},\ (\ \alpha A)_{m\text{-}1},\ \dots\ ,\ (\ \alpha^{m\text{-}1}A)_{m\text{-}1}) \cdot B^T$$

Thus,

$$C^{T} = ((A)^{T}, (\alpha A)^{T}, \dots, (\alpha^{m-1} A)^{T}) \cdot B^{T}$$

(5)

Let **M** denote the multiplication matrix  $((A)^T, (\alpha A)^T, \dots, (\alpha^{m-1}A)^T)$ , then (5) can be rewritten like below for short,

$$C^{T} = M \cdot B^{T} \tag{6}$$

Therefore, M is determinated by A and polynomial basis  $\alpha = \{1, \alpha, \alpha^2, ..., \alpha^{m-1}\}$ . Given  $\alpha^i A$ , the coefficient vector of  $\alpha^{i+1} A$  mod  $F(\alpha)$  can be computed as follows,  $\alpha^{i+1} A = \alpha \cdot \alpha^i A$  mod  $F(\alpha)$ . Obviously, the cost of generating  $\alpha^{i+1} A$  is the Hamming weight of  $F(\alpha) - 2$  XOR gates.

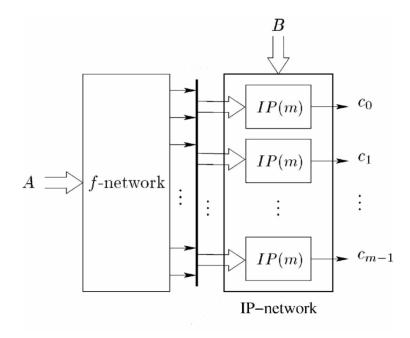

The bit parallel serial multiplier is a direct implementation based on (5). Architecture of the Mastrovito multiplier is shown in Figure 2, which comprises of two parts, one is named fnetwork, and one is named IP-network. The f-network generates the multiplication matrix **M**, which contains XOR gates only. The IP-network performs the matrix-vector multiplication as shown in (6) and consists of m inner product modules, each of these product modules consists of m AND gates and m-1 XOR gates.

Figure 2. Architecture of Bit Parallel Multiplier over GF(2<sup>m</sup>).[17]

The bit parallel multiplier essentially unrolls the 128 loops of the bit serial multiplier; therefore, the area cost is 128 times of bit serial one.

### 2.1.2.2.3 Digit Serial Multiplier

A digit serial multiplier is a compromise between the serial and parallel methods and trades off circuit area against computation time.

Let g be an integer less than m and let  $s = \lceil m/g \rceil$ . Let  $B(\alpha)$  to be separated into s pieces, each piece is organized in  $\alpha^{ig}B_i(\alpha)$ , where i and  $B_i(\alpha)$  are defined like below,

$$B_{i}(\alpha) = \sum_{j=0}^{g-1} b_{ig+j} x^{j} \quad \text{for } 0 \le i \le s-2$$

$$B_{i}(\alpha) = \sum_{j=0}^{(m \mod g)-1} b_{ig+j} x^{j}$$

for  $i = s-1$

Then the (3) can be rewritten

$$C(\alpha) = A(\alpha) (\alpha^{(s-1)g} B_{s-1}(\alpha) + \dots + \alpha^g B_1(\alpha) + B_0(\alpha)) \mod F(\alpha)$$

$$= (\dots ((A(\alpha)B_{s-1}(\alpha))\alpha^g + A(\alpha)B_{s-2}(\alpha))\alpha^g + \dots )\alpha^g + A(\alpha)B_0(\alpha) \mod F(\alpha)$$

(7)

Equation (7) can be computed using Algorithm 2.

### Algorithm 2 Digital-Serial Multiplication

Input:  $A(\alpha)$ ,  $B(\alpha)$ , and  $F(\alpha)$

Output:  $C(\alpha) = A(\alpha)B(\alpha) \mod F(\alpha)$

- 1.  $C(\alpha) \leftarrow B_{s-1}(\alpha)A(\alpha) \mod F(\alpha)$ ;

- 2. for k = s 2 downto 0 do

- 3.  $C(\alpha) \leftarrow \alpha^g C(\alpha)$ ;

- 4.  $C(\alpha) \leftarrow B_k(\alpha)A(\alpha) + C(\alpha) \mod F(\alpha)$ ;

The digital serial multiplier is implemented based on Algorithm 2. The multiplication is completed in  $\lceil m/g \rceil$  iterations which is g times faster than the bit serial multiplier, and requires fewer resources than the bit parallel multiplier.

For more detailed description with respect to digital serial multiplier, please refer to [7] in which a digit serial multiplier is proposed based on look-up tables.

# 2.2 Confidentiality Mode of Operation Background

Two modes of operation for Symmetric Key Block Ciphers, ECB and CTR, are selected to create the confidentiality in AES-GCM because they can admit pipelined, parallelized implementations and have minimal computational latency for high data rates. These modes are introduced below and more details can be obtained from [1].

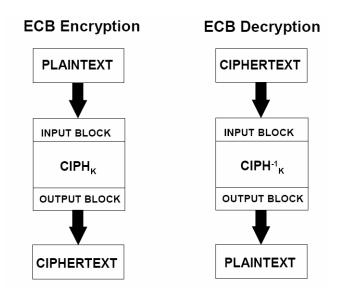

### 2.2.1 Electronic Codebook Mode (ECB)

The ECB mode is defined as follows and shown in Figure 3:

ECB Encryption:  $C_j = CIPH_K(P_j)$  for  $j = 1 \dots n$ ,

ECB Decryption:  $P_i = CIPH^{-1}_{K}(C_i)$  for  $j = 1 \dots n$ ,

where,  $CIPH_K(P_j)$  is the forward cipher function of the block cipher algorithm, such as AES, under the key K applied to the plaintext  $P_j$ ;  $CIPH^I_K(C_j)$  is the inverse cipher function of the block cipher algorithm under the key K applied to the ciphertext  $C_j$ .

Figure 3. ECB Encryption and ECB Decryption [1]

In ECB encryption and ECB decryption, multiple forward cipher functions and inverse cipher functions can be computed in parallel or pipeline. In the GCTR module of AES-GCM, ECB encryption block is embedded into a CTR block (see Figure 21).

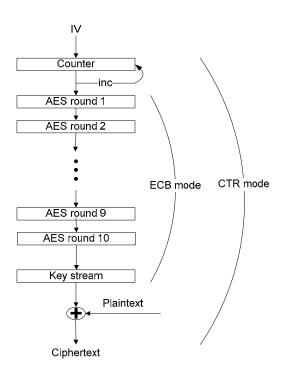

### 2.2.2 Counter Mode (CTR)

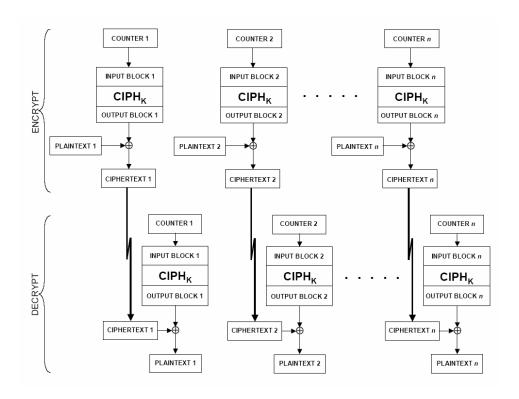

The CTR mode is a confidentiality mode also that features the application of the block cipher to a set of input data groups, called counters, to produce a set of keystreams that are XORed with the plaintext to produce the ciphertext, and vice versa. The CTR mode is defined as follows and shown in Figure 4.

CTR Encryption:

$$O_j$$

= CIPH<sub>K</sub>( $T_j$ ) for  $j$  = 1, 2 ... n;

$C_j$  =  $P_j$  XOR  $O_j$  for  $j$  = 1, 2 ... n-1;

$C_n^*$  =  $P_n^*$  XOR MSB<sub>u</sub>( $O_n$ ).

CTR Decryption:

$$O_j = CIPH_K(T_j) \text{ for } j = 1, 2 \dots n;$$

$P_j = C_j \text{ XOR } O_j \text{ for } j = 1, 2 \dots n-1;$

$P_n^* = C_n^* \text{ XOR MSB}_u(O_n).$

The symbols used in the CTR encryption and decryption are:

T<sub>j</sub>----the counters for the jth input data group,

Oi---- the key stream for the jth input data group,

P<sub>j</sub> ---- the jth plaintext group,

$C_j$ ---- the jth ciphertext group.

$\boldsymbol{C}^*_{\ n}$  ----the last group of the ciphertext, which may be a partial group.

$\boldsymbol{P}_{\ n}^{*}$  ----the last group of the plaintext, which may be a partial group.

MSB<sub>u</sub>(O<sub>n</sub>)---- the bit string consisting of the u most significant bits of the bit string O<sub>n</sub>.

In CTR encryption and CTR decryption, only the forward cipher function is invoked on each counter group, no inverse cipher function. The resulting key streams are XORed with the corresponding plaintext or ciphertext blocks to produce the ciphertext or plaintext blocks. For the last group, which may be a partial group of u bits, the most significant u bits of the last output group are used for the XOR operation; the remaining bits of the last output group are discarded. The forward cipher functions can be performed in parallel and pipelined.

Figure 4. CTR Encryption and CTR Decryption [1]

Both CTR encryption and CTR decryption are invoked in AES-GCM encryption and AES-GCM decryption, respectively.

# 2.3 Field Programmable Gate Arrays (FPGA)

The thesis presents the architecture of FPGA implementation of AES-GCM. The common implementation approaches are corresponding to three different technologies. They are:

- Application Specific Integrated Circuits (ASICs)

- Software-Programmed General Purpose CPU (SPGPC)

- Field Programmable Gate Arrays (FPGAs)

**ASIC**s are specifically designed for a fixed solution, and are thus very efficient. However, the circuit cannot be changed after fabrication. This requires a redesign of the chip if any modification needs to be done.

**SPGPC**s are a flexible solution. CPUs execute a set of instructions to perform an algorithm. By changing the software code, the functionality of the system is altered without touching the hardware. But the SPCGPC's efficiency is much lower than that of an ASIC.

**FPGA**s offer a compromise between the ASIC and the SPGPC, achieving higher performance than software, while maintaining a higher level of flexibility than hardware.

### 2.3.1 Advantages of FPGA in Cryptographic Applications

The following attributes of the FPGA technology are particularly advantageous for cryptographic applications [8].

**Algorithm Agility**: More and more security applications intend to be algorithm independent and allow switching encryption algorithms on the flying. The encryption algorithm can be chosen through the negotiation made by two communication parties.

**Algorithm Upload**: From a cryptographic point of view, algorithm upload can be necessary because a current algorithm is out of date or broken; a new algorithm is created. The security designer of the corresponding security company can upload the new bit streams of security standard to reconfigure FPGA device through the networks.

**Throughput**: Although FPGA implementations are typically slower than ASIC implementations, FPGA implementations are obviously faster than software implementations. In a cryptosystem, if a software solution is chosen for clients, then, a FPGA implementation should be adapted for servers in high-speed backbones.

**Cost Efficiency**: The production costs of an ASIC are often too high for a small number of servers in security systems. Thus, the use of FPGAs is a common alternative. Furthermore, this is the one of reasons why the FPGA is chosen for security research in institutes and universities.

Therefore, it is often best to choose an FPGA to implement cipher, such as AES-GCM standard. The CMC-FPGA-prototype-platform was chosen in this thesis for prototyping since it represents a generalized multi-core platform, appropriate for security applications. This FPGA platform will be discussed next.

## 2.3.2 FPGA VirtexII pro xc2vp100

A traditional FPGA is usually an integrated circuit consisting of

- Configurable Logic Blocks (CLBs),

- Input/Output Blocks (IOBs) and

- Programmable routing resources.

For Xilinx FPGA family VirtexII pro contains not only CLBs, IOBs, and memory arrays, but also it has IBM 400 MHz PowerPC<sup>TM</sup> processors and 622 Mbps to 6.25 Gbps full duplex serial MGT(multi-gigabit transceivers). More specifically, Table 1 shows all the main resources of the VirtexII pro xc2vp100 targeted in this thesis.

**Table 1. Virtex-II Pro Resources**

| Device   | PowerPC405<br>Processor | CLB(4  | slices)                      |                      | Block<br>SelectRAM+ |                             | DCM | Max<br>User |

|----------|-------------------------|--------|------------------------------|----------------------|---------------------|-----------------------------|-----|-------------|

|          | Blocks                  | Slices | Max<br>Distr.<br>RAM<br>(Kb) | Multiplier<br>Blocks | 18 Kb<br>Blocks     | Max<br>Block<br>RAM<br>(Kb) |     | I/O<br>Pads |

| xc2vp100 | 2                       | 44096  | 1378                         | 444                  | 444                 | 7992                        | 12  | 1164        |

# 2.3.2.1 Configurable Logic Blocks (CLBs)

The CLBs in the VirtexII pro are comprised of both combinational and sequential logic. The combinational logic can be configured to become possible Boolean functions. Flip-Flops are provided to support sequential logic and can be utilized or bypassed depending on the configuration.

One CLB has four slices. Each slice is identical and contains:

- Two function generators F and G

- Two storage elements

- Arithmetic logic gates

- multiplexers

- Fast carry look-ahead chain

### • Horizontal cascade chain

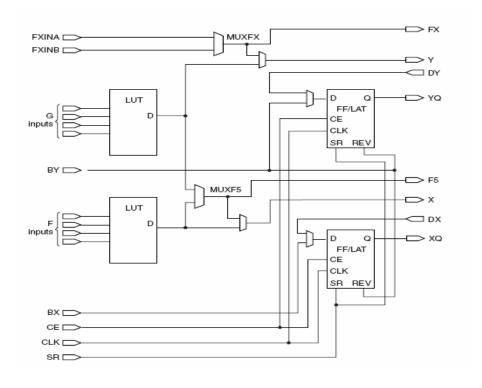

A general slice structure of VirtexII pro is shown in Figure 5. The function generators F and G can be configured as 4-input look-up tables (LUTs), as 16-bit shift registers, or as 16-bit distributed SelectRAM+ memory (to be discussed in section 2.3.2.2). The multiplexers, MUXF5 and MUXFX can provide any function of five, six, seven, or eight inputs when combined with function generators. The two storage elements can be configured either edge-triggered flip-flops or level-sensitive latches. Each CLB has internal fast interconnect and connects to a switch matrix to access general routing resources.

Figure 5. General Slice in Virtex-ll Pro [15]

### 2.3.2.2 Distributed SelectRAM+

As described in section 2.3.2.1, the Virtex-II Pro family devices feature distributed SelectRAM modules which are implemented by using function generators of the CLB resource. Distributed SelectRAM memory writes synchronously and reads asynchronously.

However, a synchronous read can be implemented using the register that is available in the same slice. One LUT can be configured as a 16x1-bit RAM which is cascadable for a deeper and wider memory implementation.

A primitive is a component in Xilinx software's library, which is available for instantiation without the need for specifying a definition in HDL code. One CLB which include 8 LUTs can be used to form up to a 128x1-bit RAM module primitive (see Table 2). These primitives are actually Distributed SelectRAM modules. Two 16 x 1 RAM resources can be combined to form a dual-port 16 x 1 RAM with one dedicated read/write port and a second read-only port. One port writes into both 16 x1 RAMs simultaneously, but the second port reads independently.

Table 2 shows the number of LUTs used in each distributed SelectRAM+ primitives.

Table 2. Resources Used by Distributed Memory [15]

| Primitive name | RAM Size   | Туре        | # of LUTs |

|----------------|------------|-------------|-----------|

| 16x1S          | 16x1 bits  | single port | 1         |

| 16x1D          | 16x1 bits  | dual port   | 2         |

| 32x1S          | 32x1 bits  | single port | 2         |

| 32x1D          | 32x1 bits  | dual port   | 4         |

| 64x1S          | 64x1 bits  | single port | 4         |

| 64x1D          | 64x1 bits  | dual port   | 8         |

| 128x1S         | 128x1 bits | single port | 8         |

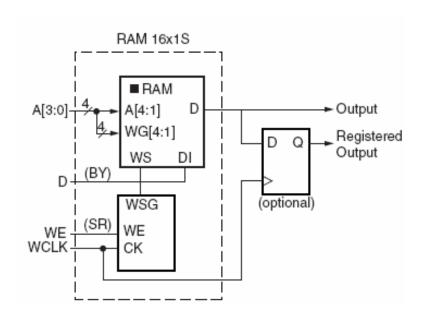

For Single-port Distributed SelectRAM+ (see Figure 6), synchronous writes address lines WG[4:1] and asynchronous reads lines A[4:1] use the same shared address lines A[3:0] from the outside.

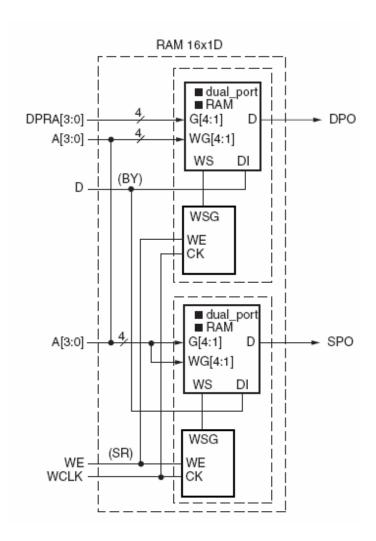

For Dual-port Distributed SelectRAM+ (see Figure 7), besides one LUT used in single-port mode, the second LUT uses the same address lines A[3:0] for synchronous write and another set of address lines DPRA[3:0] are used for the second asynchronous read.

Figure 6. Single-Port Distributed SelectRAM+ [15]

Figure 7. Dual-Port Distributed SelectRAM+ [15]

### 2.3.2.3 Block SelectRAM+

In addition to distributed memory, the Virtex-II Pro family devices include a large amount of 18 Kb block SelectRAM+ (BRAM) resources, programmable from 16K x 1 bit to 512 x 36 bit, in various depth and width configurations. These SelectRAM+ blocks are real dual-port RAM blocks which can be configured as FIFO easily. In the VirtexII pro xc2vp100, there are 444 18 Kb SelectRAM+ blocks that make it totally 1MB block SelectRAM+, Table 3 shows the supported memory configurations for single-port and dual-port modes.

**Table 3. Block SelectRAM Configuration Modes [15]**

| 16Kx1 bit | 2Kx9 bits   |

|-----------|-------------|

| 8Kx2 bits | 1Kx18 bits  |

| 4Kx4 bits | 512x36 bits |

Each port in SelectRAM+ Blocks has the following inputs: Clock, Clock Enable, Write Enable, Set/Reset, Address, and separate Data and Parity buses for inputs and outputs. Both write and read operations are synchronous.

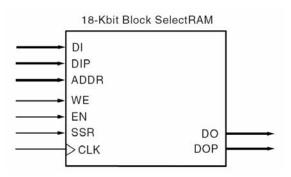

As a single-port RAM, the block SelectRAM+ has access to the 18 Kb memory locations in any of the configurations in Table 3. Each block SelectRAM+ cell is a fully synchronous memory as illustrated in Figure 8. Input data bus and output data bus widths are identical.

Figure 8. Block SelectRAM in Single-Port Mode [15]

As a dual-port RAM, each port of block SelectRAM+ has access to a common 18 Kb memory resource. These are fully synchronous ports with independent control signals for each port as illustrated in Figure 9. The data widths of the two ports can be configured independently.

Figure 9. Block SelectRAM in Dual-Port Mode[15]

Since the SelectRAM+ blocks have a regular array structure, the place-and-route tools take advantage of this feature to achieve optimum system performance and fast compile times. [15].

Distributed SelectedRAM+ and Block SelectedRAM+ are used for storage components in the AES-GCM implementation discussed in chapter 4. For example, the single port mode of the SelectedRAM+ or Block SelectedRAM+ is used to implement the S-box Look Up tables (see section 3.1.2); Also the dual port mode of the SelectedRAM+ or Block SelectedRAM+ is used to implement a 11x128-bit FIFO.

# 2.4 The CMC-Prototyping Platform

The CMC-Prototyping Platform [13][14][16][24] is a prototype system provided by Canadian Microelectronics Corporation (CMC) to Canadian universities for research purpose only. It consists of:

- AMIRIX AP1000 PCI Platform FPGA Development Board

- Xilinx Parallel-IV download cable kit and dual serial adaptor cable

- IBM Intellistation Z Pro workstation

- EDA tools for FPGA Development

- AP1000 PCI Platform FPGA Development Kit Baseline Platform

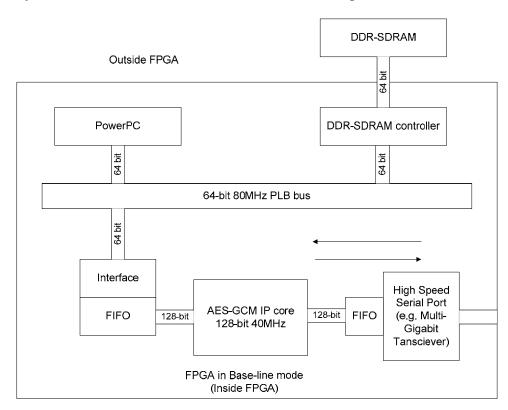

The major focus is the AP1000 FPGA Board. Figure 10 illustrates the AP1100 FPGA board hardware architecture. The DDR SDRAM banks provide 64-bit Data width for the two IBM PowerPC microprocessors which are the hardware IP cores inside the FPGA VirtexII pro xc2vp100. If the FPGA works in Base-line mode which is established by AMIRIX, all these memory blocks are controlled by the soft IP cores inside the FPGA. There are also synchronous SRAMs providing large data storage space. Configuration Flash, program Flash and System ACE are accessible through the local bus interface. The kernel driver is stored in program flash on the board. A ramdisk image is also stored in the program flash. By default, the AP1000 will load the kernel and mount the ramdisk when powered on. U-Boot which is stored in Program Flash is a bootloader program that provides the ability to load Linux, as well as a monitor program that allows access to the AP1000 resources. U-Boot is transferred to DDR-SDRAM memory for execution when it is selected to run.

The Processor Bus Dual PCI Bridge provides an interface to other devices on the local PCI bus. Through this local PCI bus, FPGA Virtex-II Pro can communicate with host PC by a PCI-to-PCI bridge device. The FPGA also has access to a PMC module if installed and an Ethernet transceiver for network access. Furthermore, the extra high-speed network interfaces can be implemented through the two Gigabit Ethernet PHY devices that are connected directly to the Virtex-II Pro if the relative soft MAC layer IP cores are downloaded to FPGA.

Expansion connectors are available through the Expansion I/O ports on the board. These expansion ports allow either cabling or custom PCB daughter cards to be directly connected

to the Virtex-II Pro. CompactFlash, Ethernet, and RS-232D connectors are accessible from outside the chassis.

The Virtex-II pro can work in either of the two work modes on CMC-prototype platform, one is called Base-line mode which is supposed to be the default mode for applying the FPGA on board; one is called Stand-alone mode which is a fully custom mode.

If the Virtex-II pro works in Base-line mode, approximately 93 % of the FPGA resources are free[24]. There are two internal buses inside it (see Figure 10), one is IBM Processor Local Bus (PLB), and one is IBM On-Chip Peripheral Bus (OPB). Two PowerPC CPU hardware IP cores and DDR-SDRAM Controller IP core are allocated on the 64-bit 80MHz PLB bus. Interrupt Controller and UART core are allocated on 32-bit 40MHz OPB bus. The PLB bus indirectly connects to the local PCI bus on the board; and the OPB bus also indirectly connects to the external local bus on the board. All these made IP cores above set up a System on a Chip (SoC) environment (i.e. so-called Base-line mode) for further application. About 7% resource of the Virtex-II pro are occupied by these IP cores.

Figure 10. AP1100 Board Architecture [24]

If the Virtex-II pro works in Stand-alone mode, all the resources on the FPGA are free for customers. Of course, no PLB bus, no OPB bus, and no SDRAM controller etc. are inside the FPGA.

# **Chapter 3**

# **Security Standard**

In this chapter, the fundamental of AES and GCM algorithms will be presented. Section 3.1 introduces the Advanced Encryption Standard (AES). Section 3.2 introduces the Galois/Counter Mode (GCM).

# 3.1 Advanced Encryption Standard (AES)

The Advanced Encryption Standard (AES) was published by NIST in 2001. AES is a symmetric block cipher that operates on 128-bit block as input and output data. The algorithm can encrypt and decrypt blocks using a secret key which has a key size of 256-bit, 192-bit, or 128-bit. One of the main features of AES is simplicity that is achieved by repeatedly combining substitution and permutation computations at different rounds. That is, AES encrypts/decrypts a 128-bit plaintext/ciphertext by repeatedly applying the same round transformation a number of times depending on the key size, see Table 4.

Table 4. Key-Block-Round Combinations [3]

|         | Key Length    | Block Size    | Number of Rounds |  |

|---------|---------------|---------------|------------------|--|

|         | (32-bit word) | (32-bit word) |                  |  |

| AES-128 | 4             | 4             | 10               |  |

| AES-192 | 6             | 4             | 12               |  |

| AES-256 | 8             | 4             | 14               |  |

The actual key size depends on the desired security level. Today, AES-128 is predominant and supported by most hardware implementations. In this section, the AES forward cipher operation (i.e. AES encryption) with 128-bit key is mainly discussed since it is invoked in the GCTR module of the AES-GCM standard to provide confidentiality.

### 3.1.1 AES Cipher

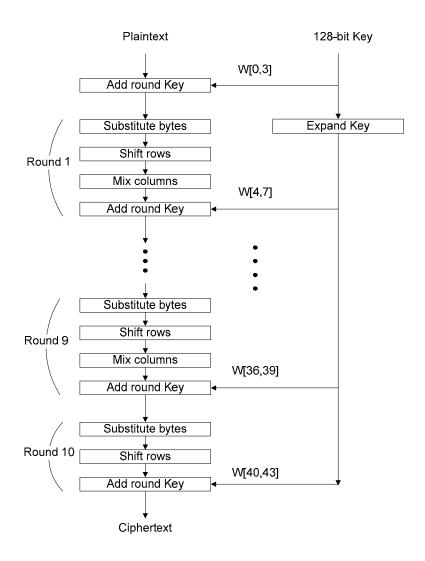

For 128-bit key size, there are 10 rounds substitutions and permutations that have to be executed in AES cipher (see Table 4). The input 128-bit plaintext is presented in a 4x4 matrix of bytes. Thus, there are 32 bits each row and each column in the matrix. This matrix is also called State array which is illustrated in Figure 11. In Figure 11,  $S_{i,j}$  indicates a byte, where  $0 \le i,j \le 3$ . The state array is altered in each round. The input key is expanded into an array of forty four 32-bit words, and each 4 words of the expanded key will be used in each round. The key expansion should be done before the cipher operation. Each round transformation consists of four phases as follows:

- SubBytes

- ShiftRows

- MixColumns

- AddRoundKey

State array

| $S_{0,0}$ | $S_{0,1}$ | $S_{0,2}$        | $S_{0,3}$ |

|-----------|-----------|------------------|-----------|

| $S_{1,0}$ | $s_{1,1}$ | $S_{1,2}$        | $S_{1,3}$ |

| $S_{2,0}$ | $S_{2,1}$ | $S_{2,2}$        | $S_{2,3}$ |

| $S_{3,0}$ | $S_{3,1}$ | S <sub>3,2</sub> | $S_{3,3}$ |

Figure 11. Illustration of State Array [3]

**SubBytes** The function SubBytes is the only non-linear function in AES. It substitutes all bytes of the state array using a LUT which is a 16x16 matrix of bytes, often called S-box. The S-box is used for SubBytes operation that contains the results of substitution and permutation of all possible 8-bit values. The content of the LUT can be computed by a finite-

field inversion followed by an affine transformation over GF(2<sup>8</sup>). Each byte of state is mapped into a byte from the S-box; The 4 leftmost bits are used as the row index while the 4 rightmost bits are used as the column index. Figure 12 illustrates the effect of the SubBytes transformation on the State array. The S-box is designed to be resistance to known cryptanalytic attacks [18]. SubBytes function has a property that the output cannot be described as a simple mathematical function of the input.

In this thesis, two schemes to implement S-box are discussed, one based on Block SelectRAM+, and one based on Distributed SelectRAM+.

Figure 12. Illustration of SubBytes Operation [3]

**ShiftRows** In the ShiftRows transformation, the bytes in the last three rows of the State are cyclically shifted over different numbers of bytes (see Figure 13). The first row is not shifted. The second row is left-shifted circularly one byte. For the third row, a 2-byte circular left shift is performed. For the forth row, a 3-byte circular left shift is performed. Since the MixColumns and AddRoundKey operations are done column by column, ShiftRows ensures that 4 bytes of one column are spread out to four different columns. Figure 13 illustrates the effect of the ShiftRows transformation on the State array.

Figure 13. Illustration of ShiftRows Transformation [3]

**MixColumns** MixColumns function operates on the state column by column. Each byte of a column in state array is mapped into a new value that is a function of all the four bytes in that column as follows:

$$\begin{bmatrix} 02 & 03 & 01 & 01 \\ 01 & 02 & 03 & 01 \\ 01 & 01 & 02 & 03 \\ 03 & 01 & 01 & 02 \end{bmatrix} \begin{bmatrix} s0,0 & s0,1 & s0,2 & s0,3 \\ s1,0 & s1,1 & s1,2 & s1,3 \\ s2,0 & s2,1 & s2,2 & s2,3 \\ s3,0 & s3,1 & s3,2 & s3,3 \end{bmatrix} = \begin{bmatrix} s'0,0 & s'0,1 & s'0,2 & s'0,3 \\ s'1,0 & s'1,1 & s'1,2 & s'1,3 \\ s'2,0 & s'2,1 & s'2,2 & s'2,3 \\ s'3,0 & s'3,1 & s'3,2 & s'3,3 \end{bmatrix}$$

MixColumns operation ensures a good mixing among the bytes of each column [18]. ShiftRows and MixColumns together ensure that after executing the rounds all output bits depend on all input bits.

**AddRoundKey** AddRoundKey operation is designed as a stream cipher; all the 128 bits of state are XORed with 4 32-bit words of expanded key resulting from key expansion. AddRoundKey is the only operation that involves using the key to ensure security.

The AES with 128-bit key size forward cipher operation is shown in Figure 14. In Figure 14, w[i,i+3] indicates 4 words of expanded key resulting from key expansion, where  $0 \le i \le 40$  (see section 3.1.2).

**Figure 14. AES Forward Cipher Operation (Pipelining Data Path)**

Decryption is a reverse of encryption which inverse round transformations to computes out the original plaintext of an encrypted ciphertext in reverse order. The round transformation of decryption uses the functions AddRoundKey, InvMixColumns, InvShiftRows, and InvSubBytes successively. AddRoundKey is its own inverse function because the XOR function is its own inverse. The round keys have to be selected in reverse order. InvMixColumns needs a different constant polynomial than Mix-Columns does. InvShiftRows rotates the bytes to the right instead of to the left. InvSubBytes reverses the S-

Box look-up table by an inverse affine transformation followed by the same inversion over GF(2<sup>8</sup>) which is used for encryption. About more details information of AES Decryption, refer to [3] and [18].

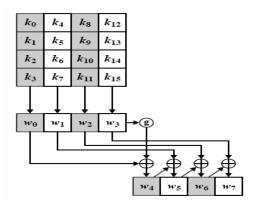

### 3.1.2 Key Expansion

The Key expansion operation takes the 128-bit key as the input for each session and yields a 44 32-bit words expanded key array as its output. In each round, AES cipher uses 4 words of the 44-word expanded key in AddRoundKey transformation, like shown in Figures 14. Figure 15 is the illustration how to expand the Key. The first 4 words of the output array is nothing but the 16-byte input secret key. Except the words whose indexes are multiple of four, the other words are simply made by XORing the preceding word with the word four positions back. The words whose indexes are multiple of four go through a more complex function, called function g before XORing with the word four positions back.

Figure 15. Key Expansion [18]

The function g takes the preceding word performs a one-byte circular left shift, then it performs SubBytes operation on each byte of the shifted result. In the last step it takes the substituted word and XORs it with a round constant hexadecimal word array "RC(i), 0, 0, 0", where,  $1 \le i \le 10$ . RC(i) is given in Table 5 in hexadecimal for each round. The purpose of

using round constants is to eliminate symmetries and similarities in making the 4-word expanded key for each round.

Table 5. Round Constant Bytes, RC in Hexadecimal [18]

| I (round number) | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 |

|------------------|----|----|----|----|----|----|----|----|----|----|

| RC(i)            | 01 | 02 | 04 | 08 | 10 | 20 | 40 | 80 | 1B | 36 |

# 3.2 Galois/Counter Mode (GCM)

The elements of GCM and the associated notation and requirements are introduced in the three sections below. The block cipher and key are discussed in Sec. 3.2.1. The data elements of the authenticated encryption and authenticated decryption functions of GCM are discussed in Sec. 3.2.2. The types of application of GCM supposed in [2] are summarized in Sec. 3.2.3. The GHASH function, GCTR function and GCM specification are described in section 3.2.4, 3.2.5 and 3.2.6, respectively.

# 3.2.1 Block Cipher

The AES-GCM standard depends on the symmetric key block cipher AES. The AES-GCM key is the block cipher key. The key shall be generated uniformly at random, or close to uniformly at random. The key should be established secretly among the parties to communicate. AES-GCM designates the encryption function of the block cipher AES as the forward cipher function denoted CIPH $_K$  which actually is AES in ECB mode (see Figure 21). GCM does not employ the inverse cipher function.

### 3.2.2 Input and Output Data

GCM consists of the two functions that are called authenticated encryption and authenticated decryption. The requirements and notation for the input and output data of these functions are introduced in Section 3.2.2.1 and 3.2.2.2.

## 3.2.2.1 Authenticated Encryption

There are three input bit streams to the authenticated encryption operation:

- A plaintext, denoted as P that can have up to2<sup>39</sup> bits;

- Additional authenticated data (AAD), denoted as A that can have up to 2<sup>64</sup> bits;

- An initialization vector denoted, as IV that can have up to  $2^{64}$  bits.

In this thesis, a 96-bit IV is adopted for efficiency following the suggestion in [12].

GCM verifies the authenticity of both P and AAD; GCM also protects the confidentiality of P, while the AAD is transmitted in the clear. The IV is a nonce that is associated with the data to be against related attack.

The following two bit strings comprise the output data of the authenticated encryption function:

- A ciphertext, denoted C, with the same bit length as that of the plaintext.

- An authentication tag, denoted T that have up to 128 bits. The T's bit length is denoted as t.

# 3.2.2.2 Authenticated Decryption

The inputs to the authenticated decryption function are values for IV, A, C, and T, as described in Sec. 3.2.2.1 above. The output is one of the following:

• The plaintext P that corresponds to the ciphertext C, or

An indication that the inputs are not authentic, denoted as FAIL.

GCM authenticated decryption computes the authentication tag T' based on received data,

and compares it with the received authentication tag T. If the two tags T and T' are equal,

then P will be the output of the authenticated decryption function. Otherwise, FAIL will be

the output.

3.2.3 Types of Applications of GCM

There are four types of applications of GCM that are recommended in SP800-380D. They are

1) GCM with an arbitrary length IV,

2) GCM with the default IV, i.e. the length of the IV is restricted to exactly 96 bits.

3) GMAC, i.e. the algorithm generates a stand-alone authentication tag T on the AAD with

the arbitrary length IV. The plaintext P is the empty string.

4) GMAC with the default IV.

In the thesis, GCM with the default IV is chosen and will be discussed in Sec. 4.

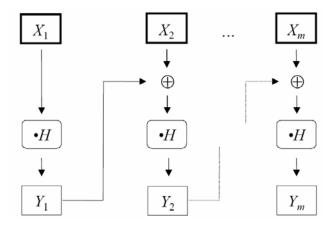

3.2.4 GHASH Function

The authentication mechanism within GCM is based on the hash function, GHASH, that

features multiplication by a fixed hash subkey, over a binary Galois field GF(2<sup>128</sup>). The hash

subkey, denoted as H, is generated by applying the block cipher to the 128-bit "0" string.

GHASH is a keyed hash function. Algorithm 3 below specifies the function that will be

invoked within the AES-GCM authenticated encryption and authenticated decryption

functions:

**Algorithm 3**: GHASH<sub>H</sub> (X)

Input:

1. Bit string X with length  $len(X) = 128 \cdot m$  for some integer m.

37

2. The hash subkey H.

# Output:

Block Y<sub>m</sub>.

## Steps:

- 1. Let  $X_1, X_2, ..., X_{m-1}, X_m$  represents the unique sequence of blocks such that  $X = X_1$   $\parallel X_2 \parallel ... \parallel X_{m-1} \parallel X_m.$

- 2. Let  $Y_0$  be the "zero block," which means  $Y_0$  is a bit string comprised by 128 binary 0.

- 3. For i=1,...,m, let  $Y_i=(Y_{i-1}\oplus X_i)\cdot H$ . where "·" indicates multiplication over finite field as discussed in chapter 2.

- 4. Return Y<sub>m</sub>.

The GHASH function is illustrated in Figure 16 below.

Figure 16. GHASH<sub>H</sub> (X1 || X2 || ... || Xm) = Ym.[2]

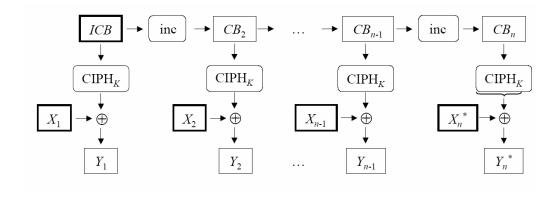

#### 3.2.5 GCTR Function

The mechanism for the confidentiality of GCM is a variation of the CTR mode (see section 2.2.2.), called GCTR, with a particular incrementing function, denoted inc, for generating the necessary sequence of counter blocks. The first counter block for the plaintext encryption is generated by incrementing a block that is derived from IV.

Algorithm 4 below specifies the GCTR function that will be invoked within the algorithms for the GCM authenticated encryption and authenticated decryption functions:

## **Algorithm 4**: GCTR<sub>K</sub> (ICB, X)

Input:

- 1. Bit string X, of arbitrary length;

- 2. Initial counter block ICB, i.e. IV or some value generated from IV;

- 3. Approved block cipher CIPH (such as AES) with a 128-bit block size;

- 4. Key K;

#### Output:

Bit string Y of bit length len(X).

#### Steps:

- 1. Let n = [Len(X)/128].

- 2. Let  $X_1, X_2, ..., X_{n-1}, X_n^*$  denote the unique sequence of bit strings such that  $X = X_1 \parallel X_2 \parallel ... \parallel X_{n-1} \parallel X_n^*$ .

- 3. Let  $CB_1 = ICB$ .

- 4. For i=2 to n, let  $CB_i = inc(CB_{i-1})$ .

- 5. For i=1 to n-1, let  $Y_i=X_i \oplus CIPH_K(CB_i)$ .

- 6. Let  $Y_n^* = X_n^* \oplus MSB_{len(X^*n)}(CIPH_K(CB_n))$ .

- 7. Let  $Y = Y_1 || Y_2 || ... || Y_{n-1} || Y_n^*$

- 8. Return Y.

#### Note:

- 1. Len(X) indicates the bit length of the bit string X.

- 2.  $X_i \parallel X_{i+1}$  indicates the concatenation of two bit strings  $X_i$  and  $X_{i+1}$ .

- 3. LSBs (X) indicates the bit string consisting of the s right-most bits of the bit string X.

- 4. MSBs (X) indicates the bit string consisting of the s left-most bits of the bit string X.

- 5. Int(X) indicates the integer for which the bit string X is a binary representation.

- 6. Inc(X) indicates the output of the GCM incrementing function applied to the block X, the more specifically,  $inc(X)=MSB_{96}(X)$   $||[(int(LSB_{32}(X))+1) mod 2^{32}]_{32}$ .

Figure 17 below illustrates the GCTR function.

Figure 17. GCTR<sub>K</sub> (ICB, X1 || X2 || ... || X\*n) = Y1 || Y2 || ... || Y\*n.[2]

## 3.2.6 GCM Specification

Algorithms for the authenticated encryption and authenticated decryption functions of GCM are specified in Section 3.2.6.1, and 3.2.6.2 below. The block cipher is AES (see section 3.1).

# 3.2.6.1 Authenticated Encryption

Algorithm 5 below performs the authenticated encryption function.

**Algorithm 5**: AES-GCM-AE<sub>K</sub> (IV, P, A)

#### Input:

- 1. Block cipher CIPH (i.e. AES) with a 128-bit block size;

- 2. Key K;

- 3. Tag length t.

- 4. Initialization vector IV;

- 5. Plaintext P;

- 6. Additional authenticated data A.

#### Output:

- 1. Cipher text C;

- 2. Authentication tag T.

#### Steps:

- 1. Let  $H = CIPH_K(0^{128})$

- 2. Define a block,  $J_0$ , as follows:  $J_0=IV||0^{31}I$ , i.e.  $J_0$  is a 128-bit string consisted of 96-bit IV, 31 '0' bits, and1 '1' bit.

- 3. Let  $C = GCTR_K(inc(J_0), P)$ .

- 4. Let  $u = 128 \cdot \lceil len(C)/128 \rceil len(C)$ , and let  $v = 128 \cdot \lceil len(A)/128 \rceil len(A)$

- 5. Define a block, S, as follows:  $S = GHASH_H(A||0^v||C||0^u||[len(A)]_{64}||[len(C)]_{64})$

- 6. Let  $T = MSB_t(GCTR_K(J_0,S))$ .

- 7. Return (C, T).

### Notes:

- 1.  $[x]_s$  indicates the binary representation of the non-negative integer x as a string of s bits, where x<2s.

- 2.  $0^{s}$  denotes the string that consists of s '0' bits. For example,  $0^{5} = B00000$ .

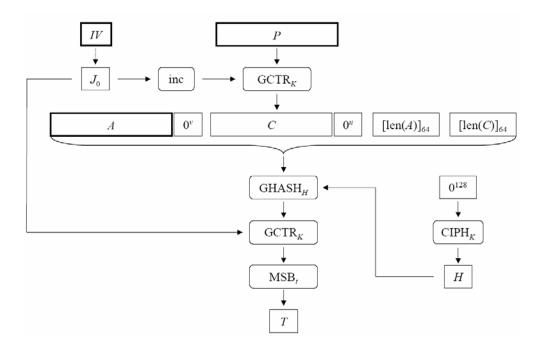

The authenticated encryption function is illustrated in Figure 18 below.

Figure 18. AES-GCM-AE<sub>K</sub> (IV, P, A) = (C, T).[2]

## 3.2.6.2 Authenticated Decryption

Algorithm 6 below performs the authenticated decryption function.

**Algorithm 6**: AES-GCM-AD<sub>K</sub> (IV, C, A, T)

# Input:

- 1. Block cipher CIPH (i.e. AES) with a 128-bit block size;

- 2. Key K;

- 3. Tag length t.

- 4. Initialization vector IV;

- 5. Cipher text C;

- 6. Additional authenticated data A.

- 7. Authentication tag T.

#### Output:

Plaintext P or indication of inauthenticity FAIL;

### Steps:

- 1. Let  $H = CIPH_K(0^{128})$

- 2. Define a block,  $J_0$ , as follows:  $J_0=IV||0^{31}l$ . i.e.  $J_0$  is a 128-bit string consisted of 96-bit IV, 31 '0' bits, and1 '1' bit.

- 3. Let  $P = GCTR_K(inc(J_0),C)$ .

- 4. Let  $u = 128 \cdot [len(C)/128] len(C)$ , and let  $v = 128 \cdot [len(A)/128] len(A)$

- 5. Define a block, S, as follows:  $S = GHASH_H(A||0^v||C||0^u||[len(A)]_{64}||[len(C)]_{64})$

- 6. Let  $T' = MSB_t(GCTR_K(J_0,S))$ .

- 7. If T = T', then return P; else return FAIL.

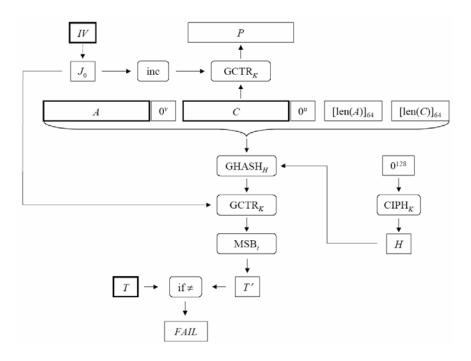

The authenticated decryption function is illustrated in Figure 19 below.

Figure 19. AES-GCM-AD<sub>K</sub> (IV, C, A, T) = P or FAIL.[2]

# **Chapter 4**

# The Architecture of AES-GCM

This chapter describes the AES-GCM implementation on the CMC-Prototype-Platform. Section 4.1 discusses the architectures of the modules of AES and GHASH, section 4.2 discusses the architectures of the AES-GCM, including IPsec data packet, and GCM data flow. Section 4.3 discusses how to verify the AES-GCM functionality.

# 4.1 Modules Design

In AES-GCM encryption and AES-GCM decryption, AES and GHASH are the basic modules which are responsible for confidentiality and authentication, respectively. In section 4.1.1, an iterative AES and fully pipelined AES are presented; in section 4.1.2, a bit serial GHASH and a bit parallel GHASH are presented. The pipelined AES and parallel-bit GHASH modules are selected for designing a high speed AES-GCM architecture discussed in section 4.2.

#### 4.1.1 AES Module

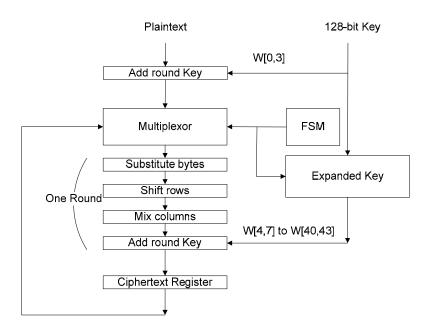

For the 128-bit key size, the AES algorithm requires calculating 10 round transformations, and each round contains four phases: SubBytes, ShiftRows, MixColumns, and AddRoundKey (see section 3.1). This allows implementing AES algorithm in either iterative method or pipelined method. In an iterative AES design, the round transformation is instantiated only once (see Figure 20). This round transformation block of hardware is used 10 times in 10 computation clock cycles while the intermediate value is stored in a register Ciphertext and used as input for the next time. A pipelined AES design can calculate all 10 rounds transformations in one clock cycle by duplicated a single round 10 times (see Figure 14). A pipelined AES architecture can be achieved by placing 128-bit registers between each

round. In large FPGAs, registers are almost free; a pipelined structure can take advantage of this feature of FPGAs.

Figure 20. AES Iterative Data Path

Table 6. Comparison between Iterative and Pipelined AES

|                                |             | Num of                            | Cost in Virte       | ex-II pro    |  |

|--------------------------------|-------------|-----------------------------------|---------------------|--------------|--|

| (expanded keys stored in CLBs) | in hardware | ciphertext per 10<br>clock cycles | With BRAM           | Without BRAM |  |

| Iterative AES                  | 1           | 1                                 | 418slices+16BRAMs   | 1678slices   |  |

| Pipelined AES                  | 10          | 10                                | 1613slices+160BRAMs | 11693slices  |  |

The control logic of both the iterative and pipelined AES architectures is implemented by using a finite state machine (FSM). Table 6 shows a rough comparison between these two approaches on throughput and cost.

In AES-GCM algorithm, the AES block is implemented in a pipelined architecture. This AES block works as a core in a hybrid from ECB and CTR mode. This hybrid actually is

GCTR(see section 3.2.5). Figure 21 shows the structure how the AES block is embedded into an ECB module and how the ECB module is embedded into a CTR module. In ECB module, AES block encrypts an input which actually is a continuously increasing counter value in CTR module, and produces the output as keystream. In CTR module, the keystream XORs a plaintext to produce output, i.e. ciphertext. After the first 10 clock cycles, the pipeline is fully filled so that the AES module can output a new 128-bit keystream every clock cycle.

Figure 21. AES CTR over ECB Mode Cipher Structure

The iterative AES can also be adopted in the AES-GCM algorithm, specifically for generating the hash subkey H. This calculation can be done in advance if the 128-bit key is known because H is nothing but the output of the iterative AES module. Therefore, it needs 10 clock cycles to generate H after inputting 128 bits '0' string into the iterative AES module.

As briefly mentioned in section 3.1.1, except for the SubBytes operation in round transformation, the ShiftRows, MixColumns, and AddRoundKey are all directly designed

using CLBs in FPGA. SubBytes which actually is a LUT operation can be designed either using CLBs (i.e single-port distributed SelectRAM+, see section 2.3.2.3) or signal-port block selectRAM+ (see section 2.3.2.4). Table 8 in section 4.2.3 shows the differences in performance and cost between AES-GCM implementations which are purely using CLBs and those using both CLBs and Block RAMs.

#### 4.1.2 GHASH Module

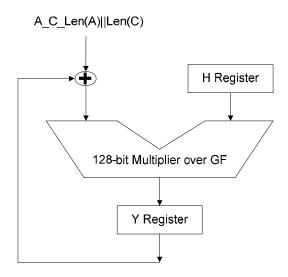

A 128-bit multiplier over  $GF(2^{128})$  is the core of the GHASH architecture. In AES-GCM, the  $GF(2^{128})$  multiplier multiplies two 128-bit operands modulo the field polynomial  $F(x) = 1 + x + x^2 + x^7 + x^{128}$  to generate a 128-bit output. The GHASH architecture is shown in Figure 22. One operand of the GF multiplier is the hash subkey H which can be treated as a fixed 128-bit constant for it will not change if the 128-bit key does not change. The Register Y whose initial value is zero holds the intermediate hash value for next step authentication computation.

Figure 22. GHASH Hardware Architecture

The architecture shown in Figure 22 is based on an iteration operation. Suppose all input data and output data are satisfied with the definitions in section 3.2.4. In the first m clock cycles, the 128-bit additional authenticated data block sequence (AAD)  $A_1$ ,  $A_2$ , ...,  $A_m$  are hashed to the GHASH through one of two inputs of XOR gates as described by algorithm 3. In the next n clock cycles, the 128-bit ciphertext block sequence  $C_1$ ,  $C_2$ , ...,  $C_{n-1}$ ,  $C_n$  are hashed to the same input of XOR gates following AAD. In the last clock cycle, 128-bit word length (A)||length(C) is hashed. Meanwhile, the intermediate hash value  $Y_i$  (see Figure 16) is fed back to another input of XOR gates to generate the another operand for the GF multiplier.

It takes m + n + 1 cycles to compute the hash value for bit parallel multiplier, and 128\*(m + n + 1) cycles for Bit Serial multiplier. There is a rough comparison listed in Table 7 between GHASH architectures using these two kinds of multipliers.

Table 7. Comparison between Different GHASH Architectures

| GHASH architecture                          | Latency (clock cycle) | Hardware complexity (k=128) | Num of Slices |

|---------------------------------------------|-----------------------|-----------------------------|---------------|

| Using Bit Serial<br>Multiplier              | 128 * (m + n + 1)     | O(k)                        | 282           |

| Using Mastrovito Bit<br>Parallel Multiplier | m + n +1              | O(k <sup>2</sup> )          | 8297          |

In order to match pipelined AES module, the GHASH module is implemented using a Mastrovito Bit Parallel GF multiplier. From a whole Mastrovito Bit Parallel GF(2<sup>128</sup>) multiplier point of view, 128<sup>2</sup> two-input AND gates and O(128<sup>2</sup>) two-input XOR gates were used for implementation. The delay from this architecture is one AND gate and 7 XOR gates. This is the critical path in the entire AES-GCM circuit design. Although a Bit Parallel multiplier over GF can be pipelined for high data rate [19], this is not the case for GHASH because the GHASH is a kind of feedback mode as mentioned in section 1.1.

# 4.2 High Speed Hardware Implementation of AES-GCM

This section describes the AES-GCM implementation. It begins by a brief introduction on the data packet structure of IPsec ESP [9] in section 4.2.1, then follows with a top level data flow description of the pipelined AES and bit parallel GHASH modules in section 4.2.2. Finally the details of the AES-GCM implementation are presented in section 4.2.3.

#### 4.2.1 Format of Data Packet of IPsec ESP

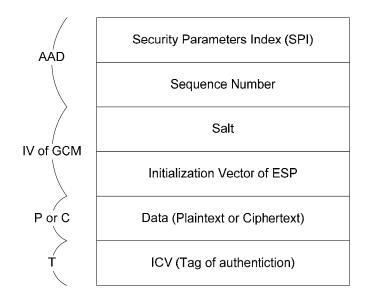

The IPsec Encapsulating Security Payload (ESP) Packet Format is shown in Figure 23. Each field in Figure 23 is explained as follows:

**Security Parameters Index (SPI)** is an arbitrary 32-bit value that uniquely identifies the Security Association for this datagram, in combination with the destination IP address and security protocol. The SPI field is mandatory.

**Sequence Number** is a 32-bit monotonically increasing counter value (sequence number). It is mandatory and is always present.

**Salt** field is also a 32-bit value that is assigned at the beginning of the security association, and then remains constant for the life of the security association. The salt should be unpredictable [10].

**ESP Payload Data** is comprised of a 64-bit initialization vector (IV of ESP), followed by the data area, along with an authentication tag T (also known as ICV) associated with the payload data.

The document in [10] clearly explains how to use AES-GCM as an IPsec ESP mechanism to provide confidentiality and data origin authentication. More specifically, the additional authentication data (AAD of Figure 23) in AES-GCM includes the SPI and Sequence Number fields; the IV of GCM includes Salt and IV of ESP fields.

Figure 23. Format of Data Packet of IPsec ESP

Information with respect to the format of data packet of IPsec ESP is provided in RFC2406[9] and RFC4106[10]. The Use of Galois-Counter Mode in IPsec ESP is shown in Figure 24.

Figure 24. The Use of GCM in IPsec ESP[11]

#### 4.2.2 Data Flow in GCM

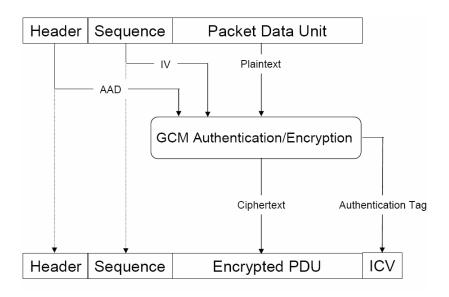

If the AES module is implemented in the pipelined architecture, the GHASH module is implemented by choosing a parallel-bit multiplier as its core, and the hash subkey H can be calculated out ahead in an iterative AES module based on a known key by each communication party. The data flow in GCM Encryption is shown in Figure 25(a); and the data flow in GCM Decryption is shown in Figure 25(b). For GCM encryption, AES-GCM starts to compute intermediate hash value  $Y_i$  when it receives additional authenticated data. It takes m clock cycles to generate  $Y_m$ . Then the GHASH has to be idle for 11 clock cycles until the first ciphertext block  $C_1$  is generated by the GCTR which is created by using a pipelined AES module. For GCM with default IV, the IV is always 96 bits long, and  $J_0$  can be created instantly by concatenation of bit strings.

The key streams for GCM encryption are created after the 10th clock cycle when  $J_0$  is input into the pipeline of GCTR. At the 11th clock cycle, cipher block  $C_1$  is generated and input to GHASH. GHASH begins to hash data again. At the m+11+n+1 clock cycle,  $Y_{m+n+1}$  is generated and XORed with  $K_0$  (i.e. CIPH<sub>K</sub>( $J_0$ )) to create authentication tag T.

Figure 25. (a) The Data Flow of GCM Encryption (b) The Data Flow of GCM Decryption

For GCM decryption, GHASH can directly compute the authentication tag T' based on AAD and ciphertext C from the input of GCM Decryption. Therefore, the max 11 clock cycles are saved compared with data flow in GCM Encryption.

#### 4.2.3 Hardware Implementation Bidirectional GCM

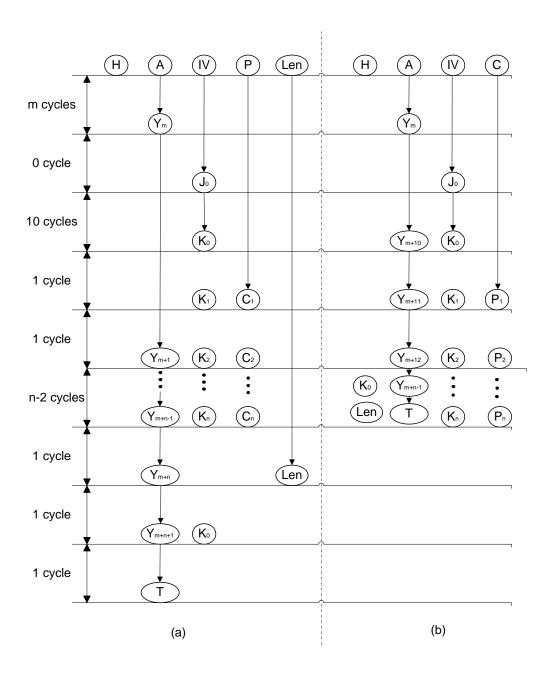

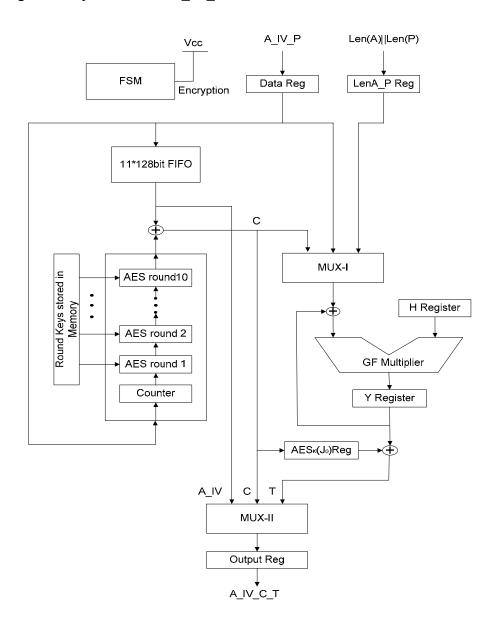

Based on the data flow analysis in section 4.2.2, a bidirectional AES-GCM hardware module is built. The "bidirectional" means: the AES-GCM module can work not only as GCM encryption but also as GCM decryption depending on the logic value of the control signal Encryption. If the Encryption signal is high, then AES-GCM works in GCM encryption mode as shown in Figure 26, otherwise, it works in GCM decryption mode.

If the Encryption signal is high, then AES-GCM works in GCM encryption mode, i.e. AES-GCM-AE (see section 3.2.6.1). In Figure 26, the data paths are 128-bit wide. The control signals do not show up except signal Encryption. They all are driven by a finite sate machine (FSM) module which is designed according to IPsec ESP packet format. The 44 32-bit round-key words are stored in a look up table instead of generated in real time. The hash subkey H is generated by an iterative AES module from the key K in advance.

A 3-to-1 multiplexer MUX-I is used whose output connects to one of the input ports of XOR gates in GHASH module. The three inputs of MUX-I are additional authenticated data AAD, ciphertext C and length information length (A) ||length(P). As discussed in section 3.2, in the first m clock cycles, the output of MUX-I is the additional authenticated data A. After 11 clock cycles, in the next n clock cycles, the output of MUX-I switches to the ciphertext C. The Final output of MUX-I is length (A) ||length(P). The first 128-bit key stream which is produced by GCTR, from the initial value IV of GCM, is stored in the  $AES_K(J_0)$  Register. This AES<sub>K</sub>(J<sub>0</sub>) Register is later used to generate the authentication tag T. Since the IV of GCM is followed by plaintext P, and the first 128-bit keystream is generated by GCTR after a delay of 10 clock cycles. Therefore, the plaintext P is delayed by 11 clock cycles in order to be encrypted by the corresponding key streams. A 11\* 128-bit FIFO meets this requirement. In the first 11 clock cycles, the data flow AAD, IV and payload data P are input to the FIFO. From the 12th clock cycle onwards, the FIFO remains in a dynamic full status by reading data out and writing new data in simultaneously until reaching the end of the IPsec ESP packet. Suffering 11 clock cycles delay through the FIFO, AAD and IV connect directly to one of the inputs of the 3-to-1 MUX-II; delayed payload data P exclusive-ORs with GCTR

output, key stream, to produce ciphertext which is connected to one input of MUX-I and MUX-II. The left input of MUX-II is the authentication tag T which is the result of GHASH final output  $Y_{m+n+1}$  XORing value in  $AES_K(J_0)$  Register. MUX-II output connects to register Output. The final output of AES-GCM-AE from register Output is data flow A\_IV\_C\_T corresponding to the input data flow A\_IV\_P.

Figure 26. AES-GCM Encryption Architecture

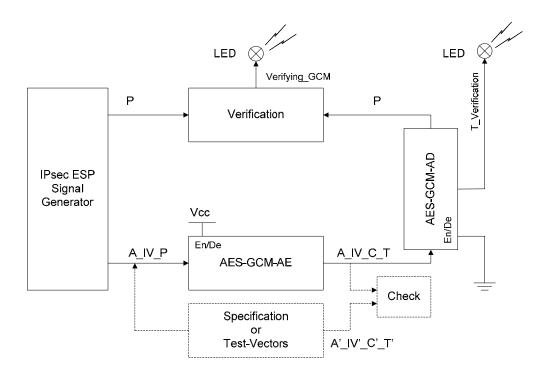

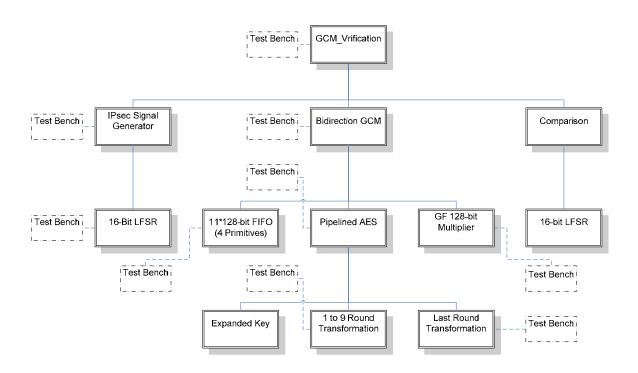

As mentioned in section 4.1.2, the critical path of this design is determined by the GHASH module. The delay of all other paths in Figure 26 is smaller than the delay produced by GHASH module.